# JEDEC STANDARD

# **Graphics Double Data Rate 7 SGRAM Standard (GDDR7)**

## **JESD239.01**

(Editorial Revision of JESD239, February 2024)

**ATTENTION USERS:** Be advised that the formulating subcommittee is working on an update that may require host design changes. Members of the subcommittee may contact the TG for more information..

**April 2024**

### JEDEC SOLID STATE TECHNOLOGY ASSOCIATION

#### **NOTICE**

JEDEC standards and publications contain material that has been prepared, reviewed, and approved through the JEDEC Board of Directors level and subsequently reviewed and approved by the JEDEC legal counsel.

JEDEC standards and publications are designed to serve the public interest through eliminating misunderstandings between manufacturers and purchasers, facilitating interchangeability and improvement of products, and assisting the purchaser in selecting and obtaining with minimum delay the proper product for use by those other than JEDEC members, whether the standard is to be used either domestically or internationally.

JEDEC standards and publications are adopted without regard to whether or not their adoption may involve patents or articles, materials, or processes. By such action JEDEC does not assume any liability to any patent owner, nor does it assume any obligation whatever to parties adopting the JEDEC standards or publications.

The information included in JEDEC standards and publications represents a sound approach to product specification and application, principally from the solid state device manufacturer viewpoint. Within the JEDEC organization there are procedures whereby a JEDEC standard or publication may be further processed and ultimately become an ANSI standard.

No claims to be in conformance with this standard may be made unless all requirements stated in the standard are met.

Inquiries, comments, and suggestions relative to the content of this JEDEC standard or publication should be addressed to JEDEC at the address below, or refer to www.jedec.org under Standards and Documents for alternative contact information.

Published by

©JEDEC Solid State Technology Association 2024

3103 10th Street North

Suite 240S

Arlington, VA 22201

JEDEC retains the copyright on this material. By downloading this file, the individual agrees not to charge for or resell the resulting material.

**PRICE: Contact JEDEC**

Printed in the U.S.A.

All rights reserved

### **ATTENTION USERS**

Be advised that the formulating subcommittee is working on an update that may require host design changes. Members of the subcommittee may contact the TG for more information.

### **Graphics Double Data Rate 7 SGRAM Standard (GDDR7)**

### **Contents**

|   |           |                                                  | Pages |

|---|-----------|--------------------------------------------------|-------|

| 1 | Scope     |                                                  | 1     |

| 2 | Overvie   | w, Definitions, and Organization                 | 2     |

|   | 2.1       | Features                                         | 2     |

|   | 2.2       | Functional Description                           | 3     |

|   | 2.3       | Definition Of Signal State Terminology           | 4     |

|   | 2.4       | Clocking                                         | 5     |

|   | 2.5       | Addressing                                       | 8     |

|   | 2.6       | Command Address Bus Inversion (CABI)             | 9     |

|   | 2.7       | Command Address Parity (CAPAR) Definition        | 9     |

|   | 2.8       | CABI and CAPAR Order                             | 10    |

|   | 2.9       | PAM3                                             | 11    |

|   | 2.9.      | 1 PAM3 Signaling and Encoding Conventions        | 11    |

|   | 2.9.      | 2 PAM3 Burst Encoding                            | 11    |

|   | 2.9.      |                                                  |       |

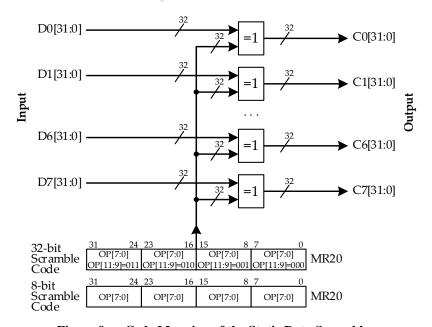

|   | 2.10      | Static Data Scrambler                            | 25    |

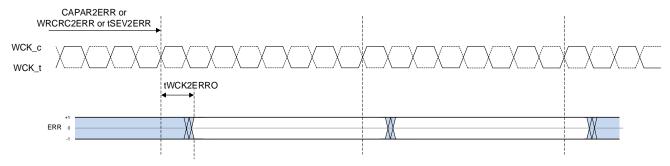

|   | 2.11      | ERR Signal                                       | 26    |

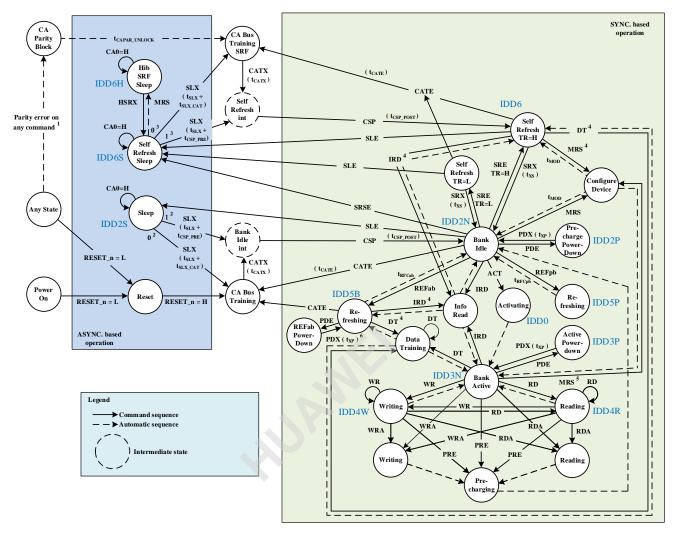

|   | 2.12      | Simplified State Diagram                         | 29    |

| 3 | Initializ | ation and Power-Off                              | 31    |

|   | 3.1       | Power-Up Initialization                          | 31    |

|   | 3.2       | Initialization With Stable Power                 | 35    |

|   | 3.3       | Controlled Power-Off Sequence                    | 36    |

|   | 3.4       | Operating Voltages During Power-Up And Power-Off | 36    |

| 4 | Mode R    | egisters                                         | 37    |

|   | 4.1       | Mode Register Assignment and Definition          | 40    |

|   | 4.1.      | 1 MR0                                            | 40    |

|   | 4.1.      | 2 MR1                                            | 41    |

|   | 4.1.      | 3 MR2                                            | 42    |

|   | 4.1.      | 4 MR3                                            | 43    |

|   | 4.1.      | 5 MR4                                            | 43    |

|   | 4.1.      | 6 MR5                                            | 44    |

|   |     | 4.1.7  | MR6                           | . 46 |

|---|-----|--------|-------------------------------|------|

|   |     | 4.1.8  | MR7                           | . 47 |

|   |     | 4.1.9  | MR8                           | . 48 |

|   |     | 4.1.10 | MR9                           | . 49 |

|   |     | 4.1.11 | MR10                          | . 50 |

|   |     | 4.1.12 | MR11                          | . 50 |

|   |     | 4.1.13 | MR12                          | . 51 |

|   |     | 4.1.14 | MR13                          | . 52 |

|   |     | 4.1.15 | MR14                          | . 53 |

|   |     | 4.1.16 | MR15                          | . 55 |

|   |     | 4.1.17 | MR16                          | . 56 |

|   |     | 4.1.18 | MR17                          | . 57 |

|   |     | 4.1.19 | MR18                          | . 61 |

|   |     | 4.1.20 | MR19                          | . 62 |

|   |     | 4.1.21 | MR20                          | . 63 |

|   |     | 4.1.22 | MR21                          | . 63 |

|   |     | 4.1.23 | MR22                          | . 64 |

|   |     | 4.1.24 | MR23                          | . 65 |

|   |     | 4.1.25 | MR24                          | . 66 |

|   |     | 4.1.26 | MR25                          | . 66 |

|   |     | 4.1.27 | MR26                          | . 67 |

|   |     | 4.1.28 | MR27                          | . 68 |

|   |     | 4.1.29 | MR28                          | . 68 |

|   |     | 4.1.30 | MR29                          | . 69 |

|   |     | 4.1.31 | MR30                          | . 69 |

|   |     | 4.1.32 | MR31                          | . 70 |

|   | 4.2 | Me     | ode Register Default Settings | .70  |

| 5 | Tra | ining  |                               | . 72 |

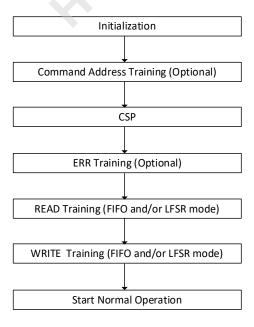

|   | 5.1 | Int    | erface Training Sequence      | .72  |

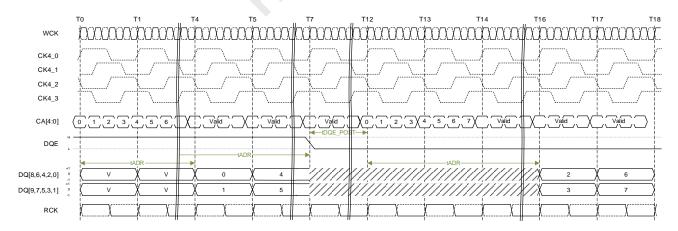

|   | 5.2 | Co     | ommand Address Bus Training   | .73  |

|   | 5.3 | EF     | RR Training                   | .79  |

|   | 5.4 | Da     | ıta Training                  | .81  |

|   |     | 5.4.1  | Data Training Common Features | . 81 |

|   |      | 5.4.2   | Read Training                                                       | 96  |

|---|------|---------|---------------------------------------------------------------------|-----|

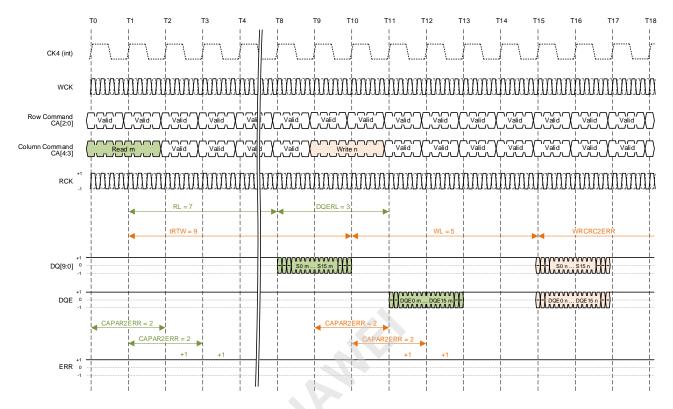

|   |      | 5.4.3   | Write Training                                                      | 103 |

|   | 5.5  | C       | Command Address Oscillator (CAOSC)                                  | 111 |

|   |      | 5.5.1   | tWCK2CA Offset due to Temperature and Voltage Variation             | 114 |

|   |      | 5.5.2   | CAOSC_Run and CAOSC_Count Registers                                 | 114 |

|   | 5.6  | Г       | Outy Cycle Corrector (DCC)                                          | 116 |

| 6 | Ope  | eration |                                                                     | 117 |

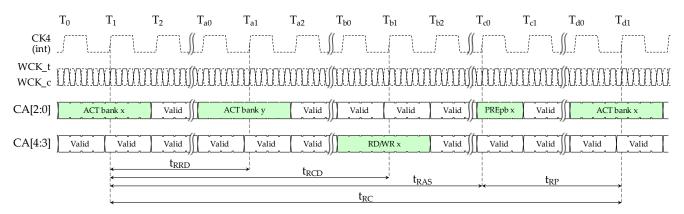

|   | 6.1  | R       | ow And Column Commands                                              | 117 |

|   | 6.2  | C       | Command Truth Table                                                 | 118 |

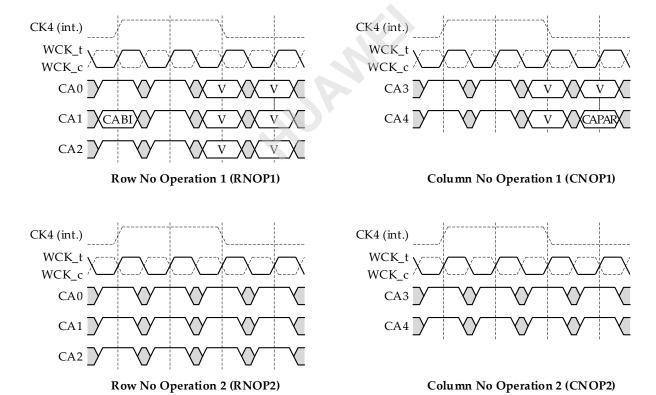

|   | 6.3  | N       | IOP                                                                 | 123 |

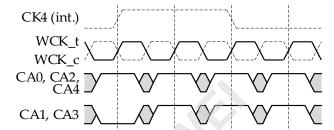

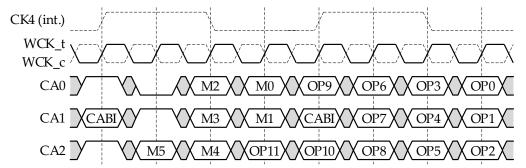

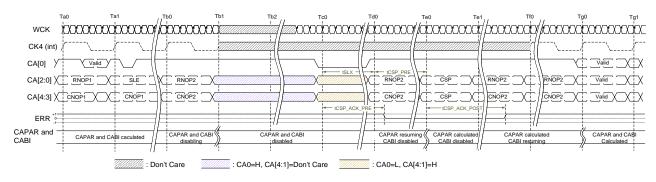

|   | 6.4  | C       | Command Start Point (CSP)                                           | 124 |

|   | 6.5  | N       | Mode Register Set (MRS)                                             | 126 |

|   | 6.6  | Iı      | nfo Read                                                            | 128 |

|   |      | 6.6.1   | Temperature Sensor Readout                                          | 134 |

|   |      | 6.6.2   | Maximum Temperature Log                                             | 135 |

|   |      | 6.6.3   | hPPR Resources                                                      |     |

|   |      | 6.6.4   | Serial ID                                                           | 135 |

|   | 6.7  | R       | ow Activation                                                       |     |

|   |      | 6.7.1   | Additional Requirements Concerning a Non-Existing Row Address Range | 137 |

|   | 6.8  | V       | Vrite                                                               | 138 |

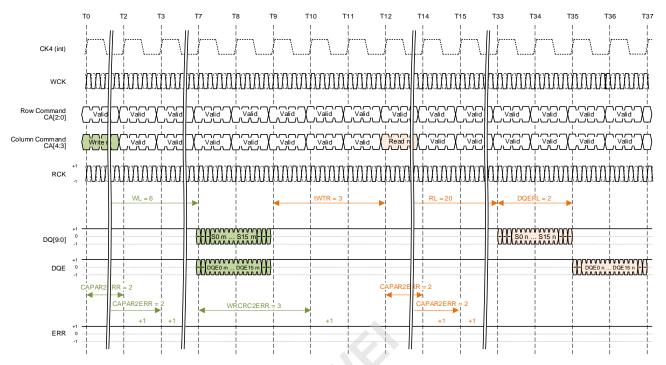

|   | 6.9  | R       | ead Clock (RCK)                                                     | 153 |

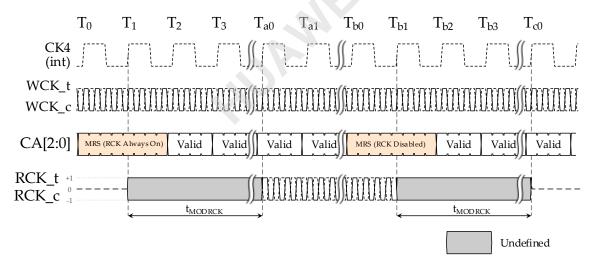

|   |      | 6.9.1   | RCK Always On                                                       | 154 |

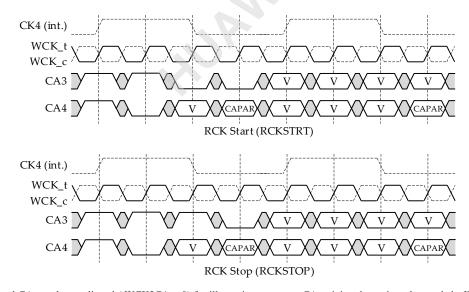

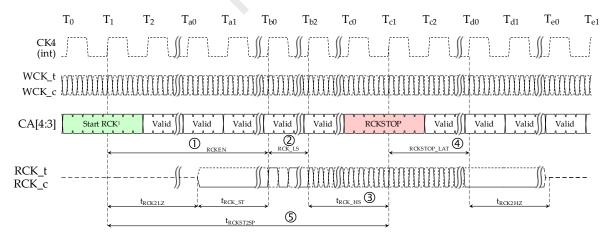

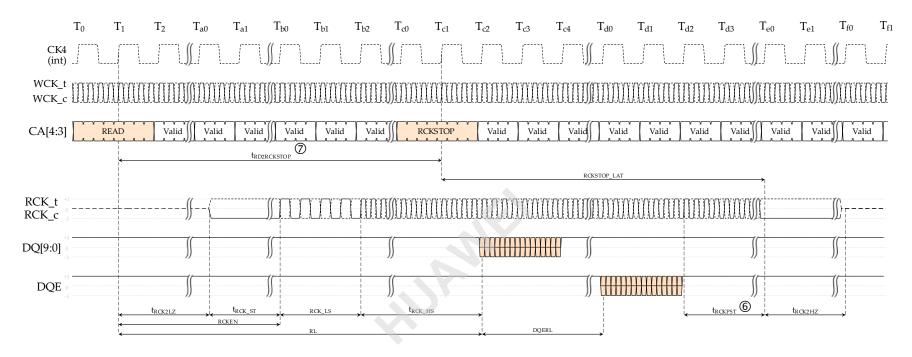

|   |      | 6.9.2   | RCK Start/Stop Modes                                                | 155 |

|   | 6.10 | ) R     | ead                                                                 | 163 |

|   | 6.11 | l R     | ow Precharge                                                        | 180 |

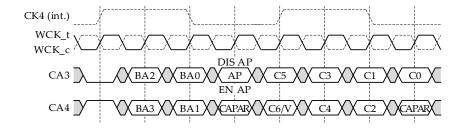

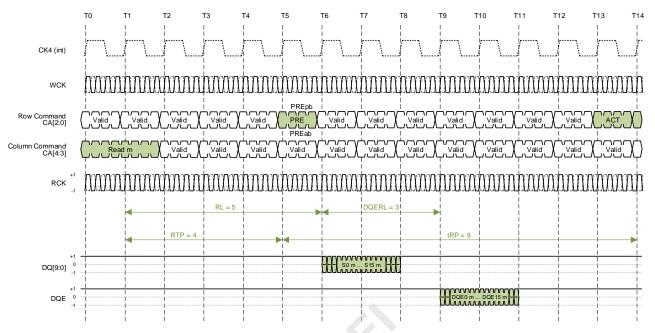

|   |      | 6.11.1  | Auto Precharge                                                      | 180 |

|   | 6.12 | 2 R     | efresh                                                              | 182 |

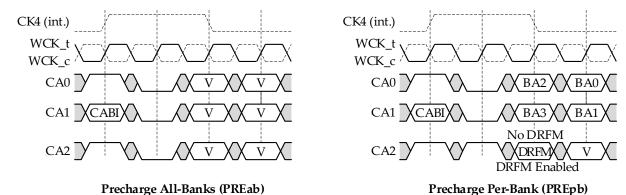

|   |      | 6.12.1  | Refresh All-Bank (REFab) Command                                    | 182 |

|   |      | 6.12.2  | Refresh Per-Bank (REFpb) Command                                    | 184 |

|   | 6.13 | 3 R     | efresh Management (RFM)                                             | 188 |

|   |      | 6.13.1  | Adaptive Refresh Management (ARFM)                                  | 191 |

|   |      | 6.13.2  | Directed Refresh Management (DRFM)                                  | 193 |

|   | 6.14 | 1 9     | elf Refresh                                                         | 195 |

|    | 6.15 | Sleep Modes                                         | 198 |

|----|------|-----------------------------------------------------|-----|

|    | (    | 6.15.1 Hibernate Self Refresh Sleep Mode            | 202 |

|    | 6.16 | Power-Down                                          | 203 |

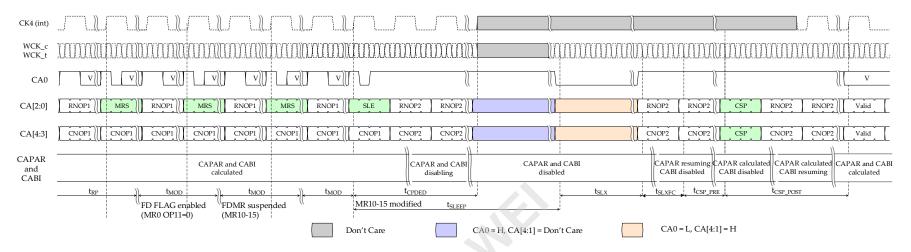

|    | 6.17 | Frequency Change Sequence (fWCK)                    | 205 |

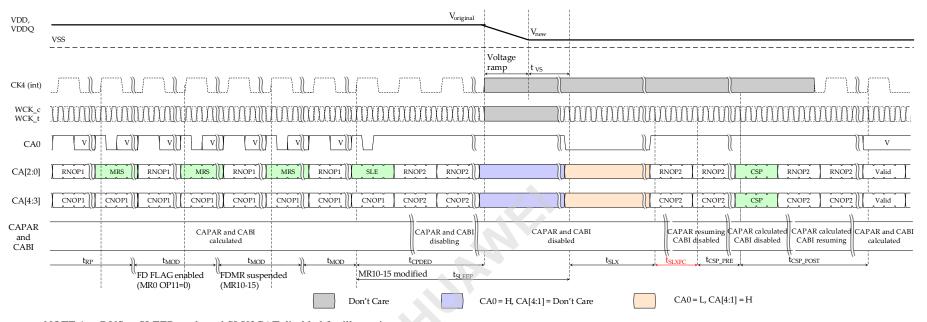

|    | 6.18 | Dynamic Voltage Sequence (DVS)                      | 207 |

| 7  | Data | Integrity                                           | 209 |

|    | 7.1  | Read and Write CRC                                  | 210 |

|    | 7.2  | On-Die ECC                                          | 214 |

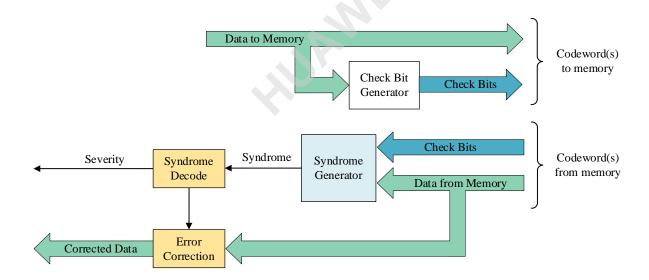

|    | ,    | 7.2.1 On_Die ECC Overview                           | 214 |

|    | ,    | 7.2.2 On-Die ECC Requirements                       | 215 |

|    | ,    | 7.2.3 DRAM Fault Isolation Requirements             | 215 |

|    | ,    | 7.2.4 Poison                                        | 215 |

|    | ,    | 7.2.5 On-Die ECC Transparency Protocol              | 216 |

|    | ,    | 7.2.6 Error Check and Scrub (Auto ECS)              |     |

|    | 7.3  | ECC Engine Test Mode                                | 223 |

|    | 7.4  | Command Address Parity (CAPAR) Protocol             | 228 |

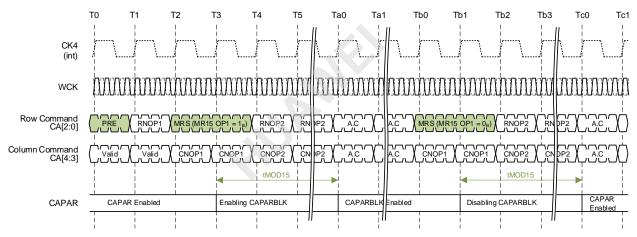

|    | 7.5  | CAPAR with Command Blocking (CAPARBLK)              |     |

|    | 7.6  | CSP Feedback                                        | 239 |

|    | 7.7  | Hard Post Package Repair (hPPR)                     | 246 |

|    | ,    | 7.7.1 hPPR Fail Row Address Repair                  | 248 |

|    | ,    | 7.7.2 hPPR Required Timing Parameters               | 249 |

| 8  | Oper | rating Conditions                                   | 250 |

|    | 8.1  | Absolute Maximum Ratings                            | 250 |

|    | 8.2  | Pad Capacitances                                    | 250 |

|    | 8.3  | Package Electrical Specification                    | 251 |

|    | 8.4  | Package Thermal Characteristics                     | 251 |

|    | 8.5  | Electrostatic Discharge Sensitivity Characteristics | 252 |

|    | 8.6  | Operating Temperature Range                         | 252 |

|    | 8.7  | DC Operating Conditions                             | 253 |

|    | 8.8  | AC Operating Conditions                             | 255 |

| 9  | IDD  |                                                     | 256 |

| 10 | AC T | Timings                                             | 276 |

| 11 | Pack | age Specification                                   | 291 |

| 11.1          | Signals                                                             | 291   |

|---------------|---------------------------------------------------------------------|-------|

| 11.2          | Ball-Out                                                            | 292   |

| 11.3          | DQ Map Mode                                                         | 294   |

| 11.4          | Package Outline                                                     | 296   |

| 11.5          | 2-Channel Mode Enable                                               | 297   |

| Annex A —     | (Informative) Differences between Document Revisions                | 301   |

| List of Eigen | <b></b>                                                             |       |

| List of Figu  | res                                                                 | Pages |

| Figure 1 —    | GDDR7 Clocking and Interface Relationship                           |       |

| -             | Block Diagram of an Example Clock System                            |       |

| -             | Example of Command Address Bus Inversion Logic                      |       |

| Figure 4 —    | Command Address Bus Inversion (CABI) and Command Address Parity (Ca | APAR) |

|               | Flow Diagram                                                        |       |

|               | Burst Data Payload Encoding Diagram (Read Operation)                |       |

| -             | Burst Data Payload Decoding Diagram (Write Operation)               |       |

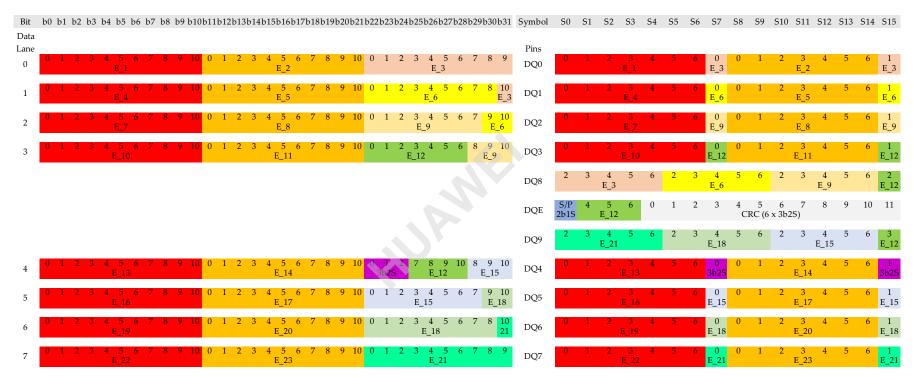

| •             | PAM3 Burst Data Mapping                                             |       |

| -             | RTL Code Implementation of the 11b7S Encoder/Decoder                |       |

| _             | Code Mapping of the Static Data Scrambler                           |       |

| Figure 10 —   | - ERR Lane Timing                                                   | 28    |

|               | - Simplified State Diagram                                          |       |

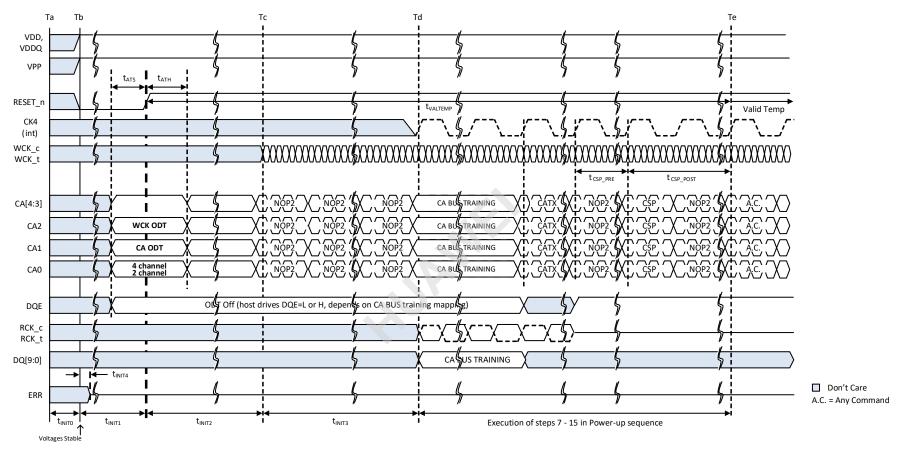

| Figure 12 —   | - Power-up Initialization                                           | 33    |

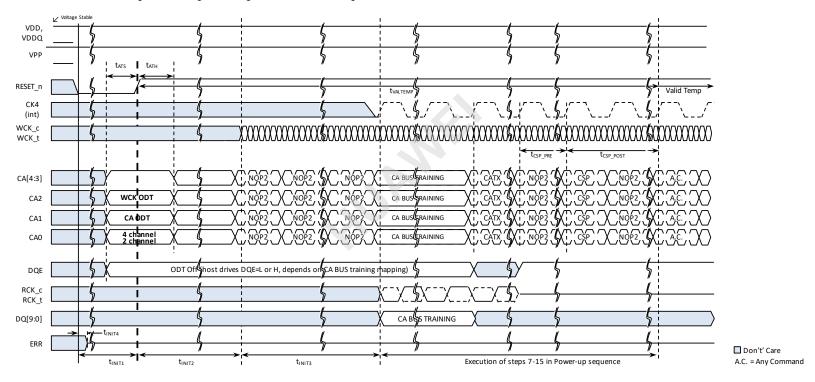

| Figure 13 —   | - Initialization with Stable Power                                  | 35    |

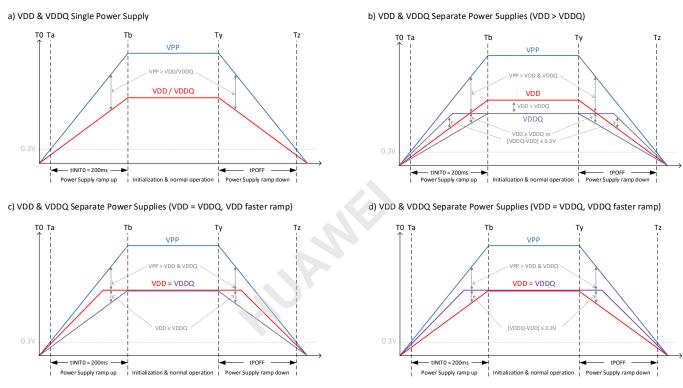

| Figure 14 —   | - Examples of Power Supply Ramp-Up and Ramp-Down                    | 36    |

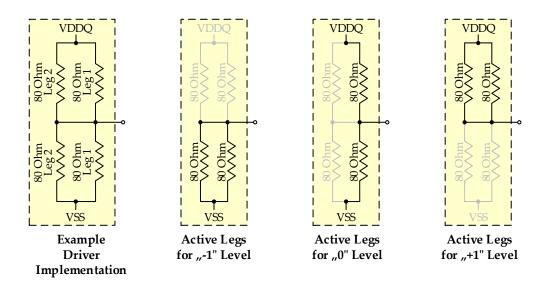

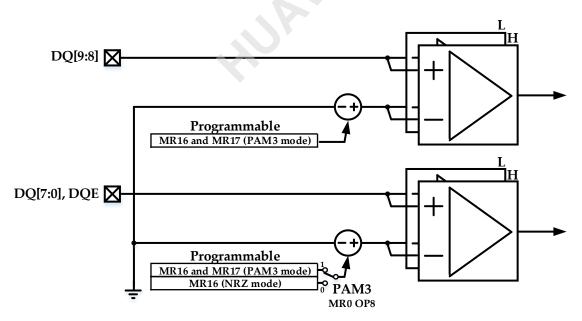

| Figure 15 —   | - Example Driver Implementation and Active Legs in PAM3 Mode        | 46    |

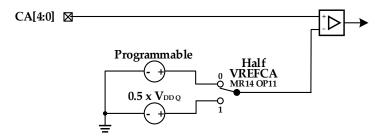

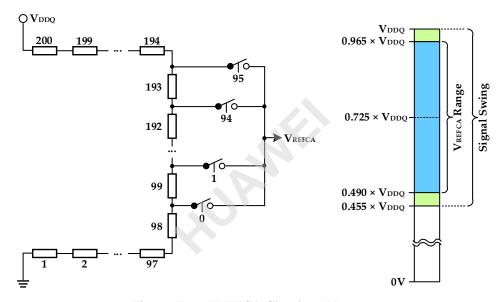

| Figure 16 —   | - VREFCA Options                                                    | 54    |

| Figure 17 —   | - VREFCA Circuit and Range                                          | 54    |

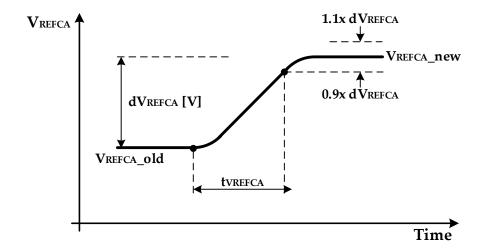

| Figure 18 —   | - VREFCA Settling Time                                              | 54    |

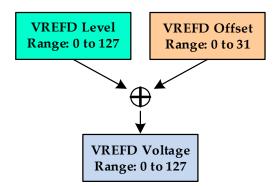

| Figure 19 —   | - VREFD Options                                                     | 58    |

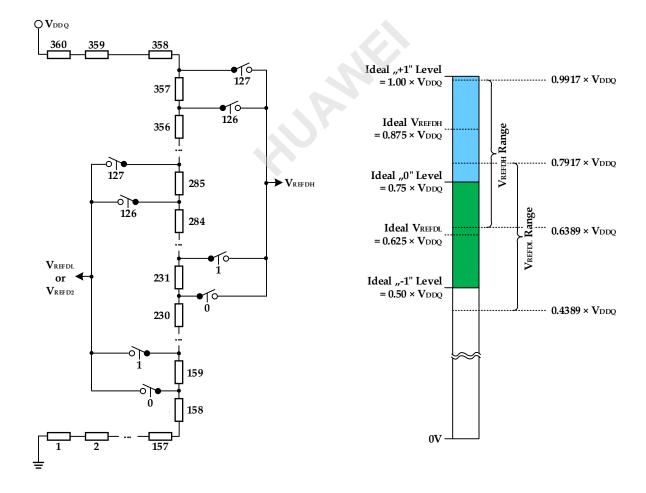

| Figure 20 —   | - VREFDL and VREFDH Levels and Offsets in PAM3 Mode                 | 59    |

| Figure 21 —   | - VREFDL, VREFDH, and VREFD2 Circuit and Ranges                     | 59    |

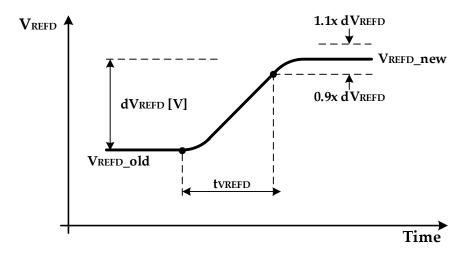

| Figure 22 —   | - VREFD Settling Time                                               | 60    |

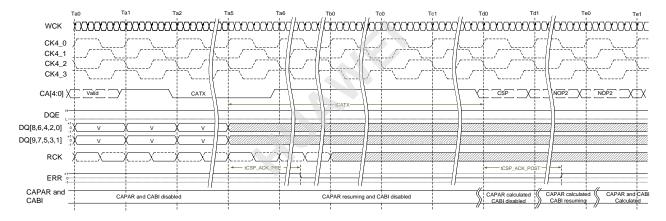

| Figure 23 —   | - Interface Training Sequence                                       | 72    |

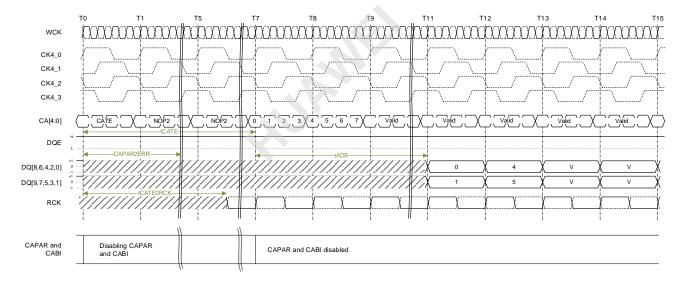

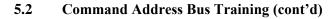

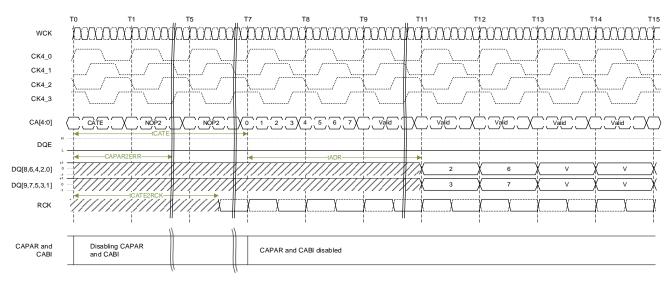

| Figure 24 — CA Training Entry and CK4_0 / CK4_1 Sampling                                                                                                             | 74  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 25 — CA Training and CK4_2 / CK4_3 Sampling                                                                                                                   | 75  |

| Figure 26 — DQE Change to Select Alternate CK4 Phases.                                                                                                               | 75  |

| Figure 27 — CA Training Exit                                                                                                                                         | 76  |

| Figure 28 — SLX to CA Training Entry                                                                                                                                 | 76  |

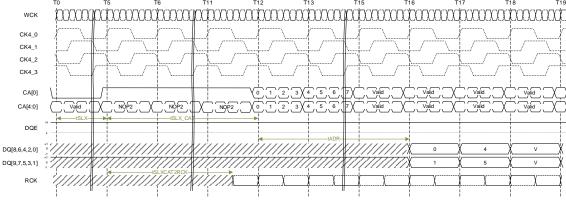

| Figure 29 — CA Parity Error to CA Training Entry                                                                                                                     | 77  |

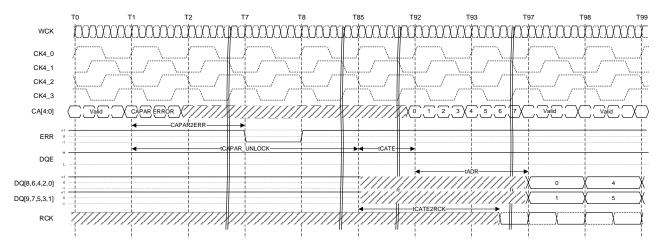

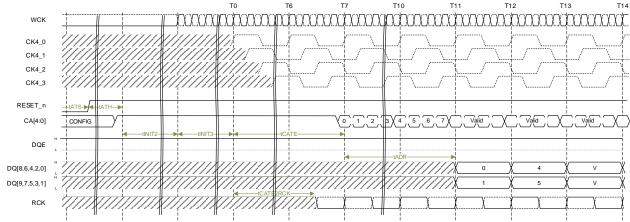

| Figure 30 — RESET Deassertion to CA Training Entry                                                                                                                   | 78  |

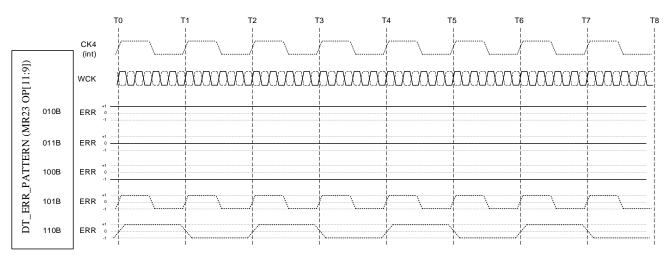

| Figure 31 — ERR Training Patterns                                                                                                                                    | 80  |

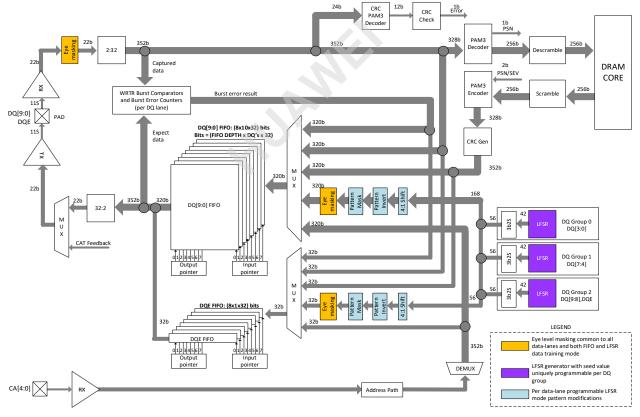

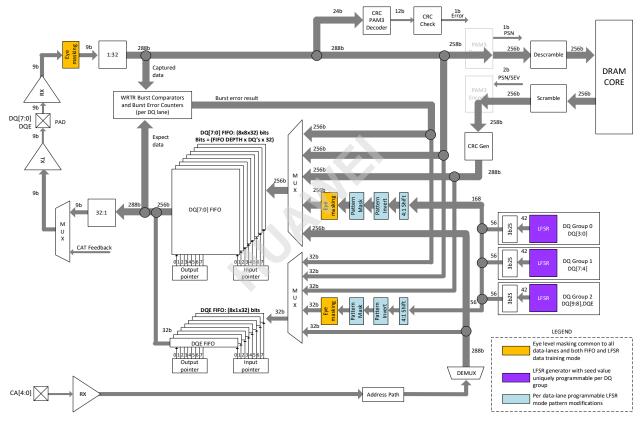

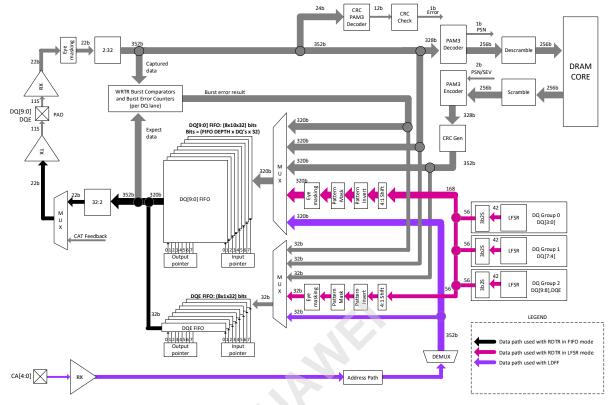

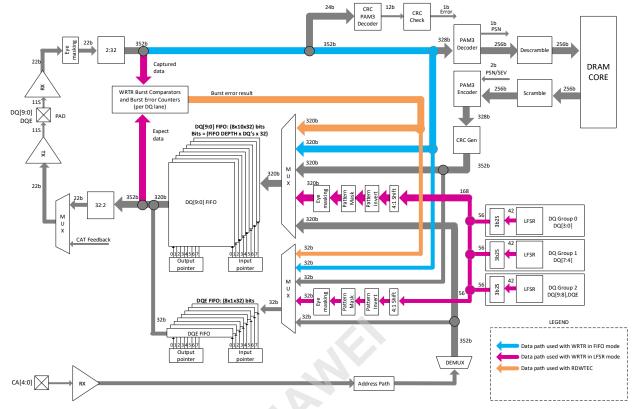

| Figure 32 — Data Paths Used for Read and Write Trainings                                                                                                             | 82  |

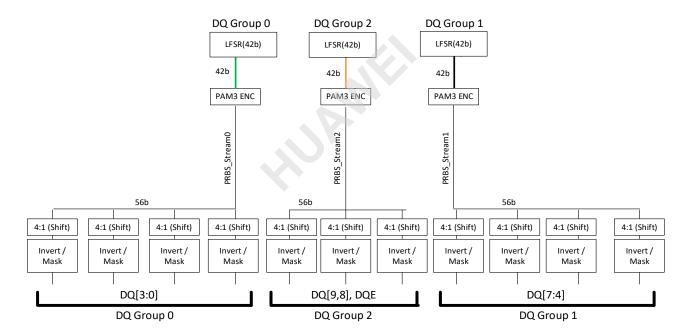

| Figure 33 — Write Training LFSR DQ Groups                                                                                                                            | 85  |

| Figure 34 — LFSR to 3b2S Encoder Mapping                                                                                                                             | 86  |

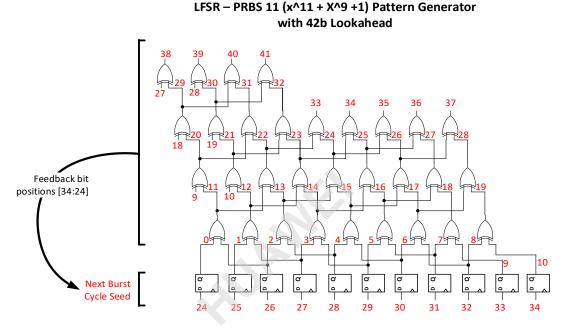

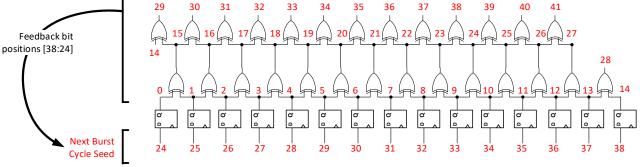

| Figure 35 — Example LFSR PRBS11 Pattern Generator                                                                                                                    | 89  |

| Figure 36 — Example LFSR PRBS15 Pattern Generator                                                                                                                    | 90  |

| Figure 37 — NRZ Mode Data Paths Used for Read and Write Trainings                                                                                                    | 95  |

| Figure 38 — Data Paths used for Read Training                                                                                                                        |     |

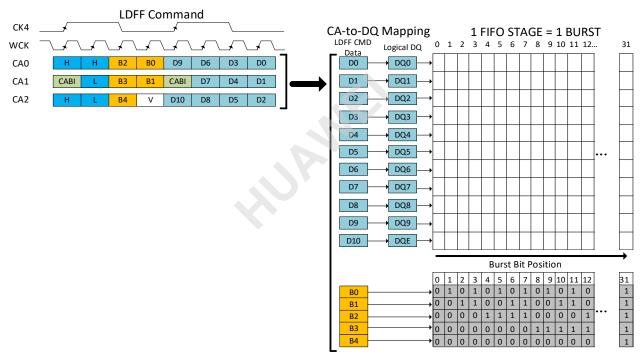

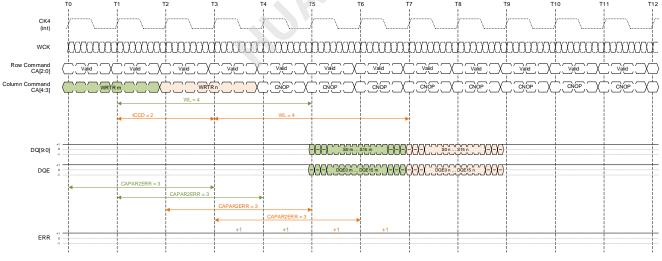

| Figure 39 — LDFF Command                                                                                                                                             | 98  |

| Figure 40 — LDFF Command Address to DQE and DQ[9:0] Mapping                                                                                                          | 98  |

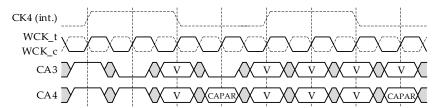

| Figure 41 — RDTR Command                                                                                                                                             | 99  |

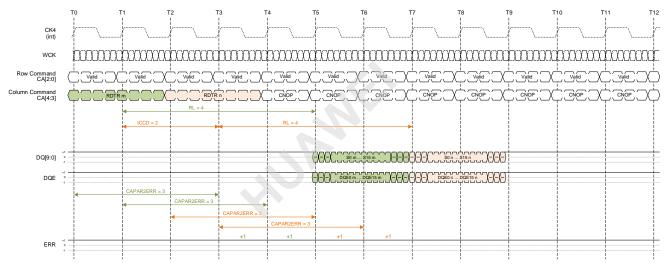

| Figure 42 — Gapless Read Training Commands                                                                                                                           | 100 |

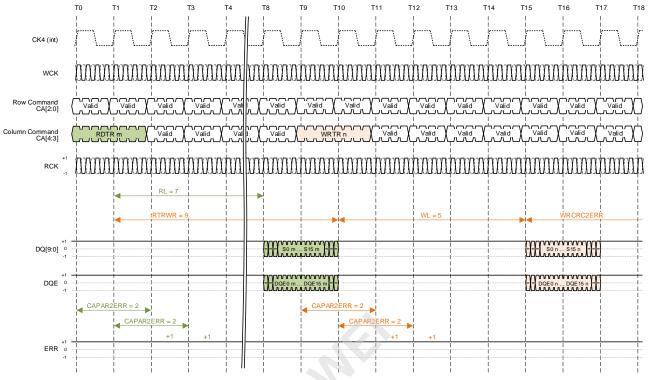

| Figure 43 — RDTR to WRTR Command                                                                                                                                     | 101 |

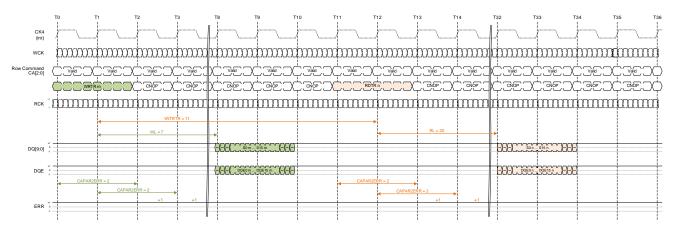

| Figure 44 — WRTR Command                                                                                                                                             | 104 |

| Figure 45 — WRTR to RDTR Command                                                                                                                                     | 105 |

| Figure 46 — Gapless Write Training Commands                                                                                                                          | 105 |

| Figure 47 — Data Paths used for Write Training                                                                                                                       | 106 |

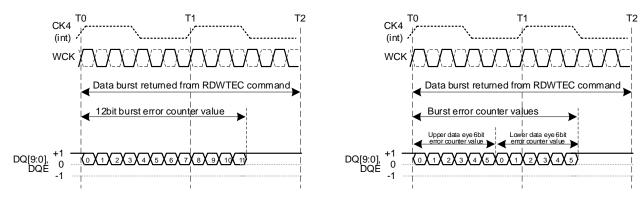

| Figure 48 — RDWTEC Command                                                                                                                                           | 109 |

| Figure 49 — Burst Error Counter Data Returned using RDWTEC Command in Single 12-bit Burst Error Counter Mode (Left) and Dual 6-bit Burst Error Counter Mode (Right). | 109 |

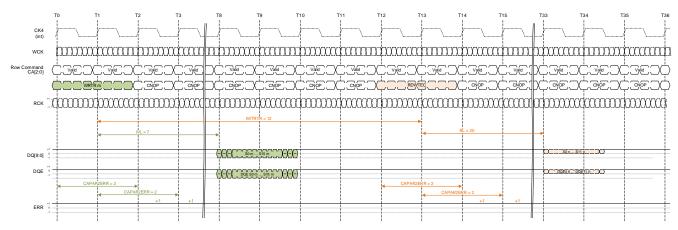

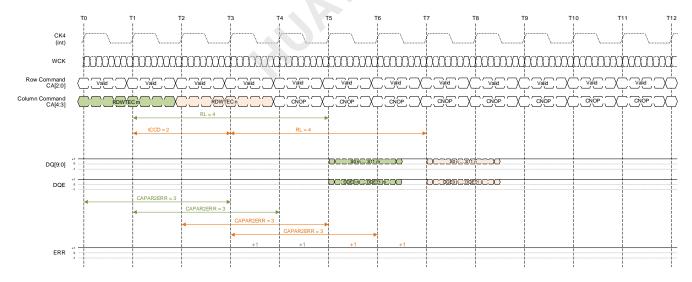

| Figure 50 — Write Training using WRTR and RDWTEC Commands in LFSR Training Mode                                                                                      | 110 |

| Figure 51 — Gapless RDWTEC Commands in LFSR Training Mode                                                                                                            | 110 |

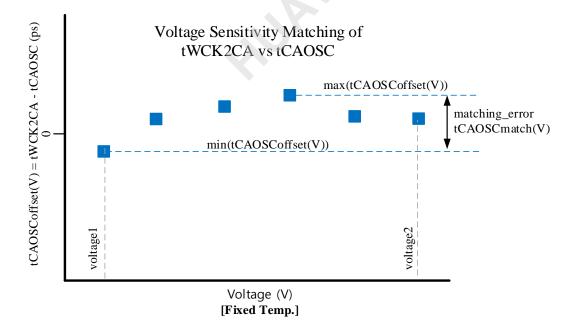

| Figure 52 — CA Oscillator Offset (tCAOSCoffset(V))                                                                                                                   | 112 |

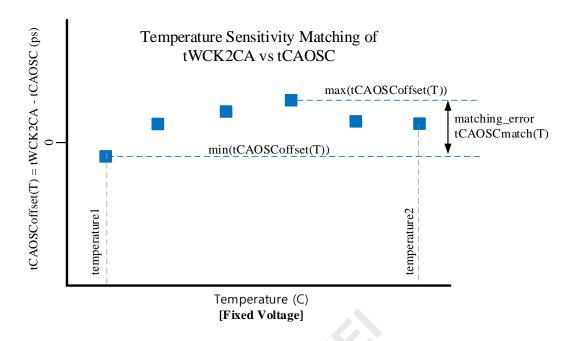

| Figure 53 — Oscillator Offset (tCAOSCoffset(T))                                                                                                                      | 113 |

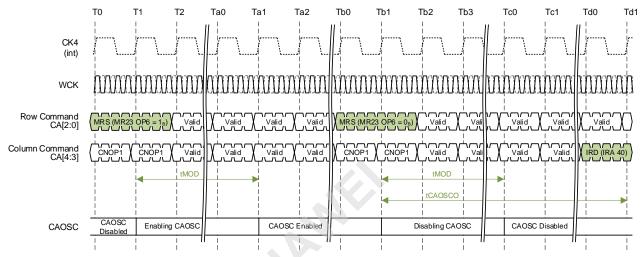

| Figure 54 — CAOSC Stop to IRD (tCAOSCO)                                                                                                                              | 115 |

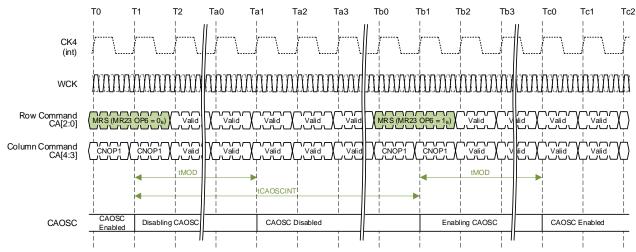

| Figure 55 — CAOSC Stop to CAOSC Start (tCAOSCINT)                                                                                                                    | 115 |

| Figure 56 — Row and Column No Operation Commands                                                                                                                     | 123 |

| Figure 57 – | - Command Start Point Command                                                      | 124 |

|-------------|------------------------------------------------------------------------------------|-----|

| Figure 58 – | - CSP Command Operation                                                            | 125 |

| Figure 59 – | - Mode Register Set Command                                                        | 126 |

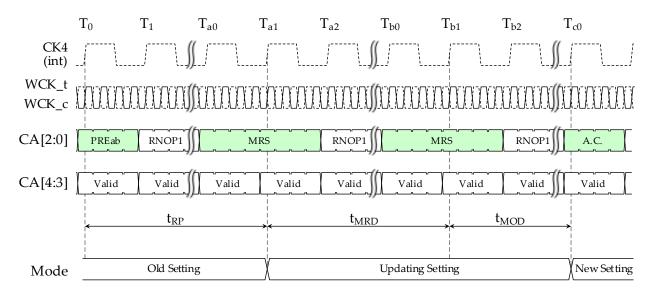

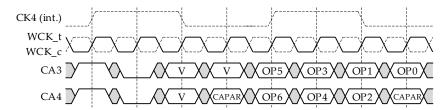

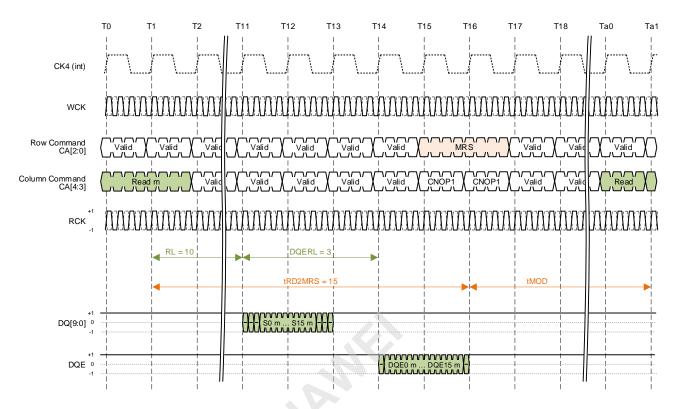

| Figure 60 – | – Mode Register Set Timings                                                        | 127 |

| Figure 61 – | - Info Read Command (IRD)                                                          | 128 |

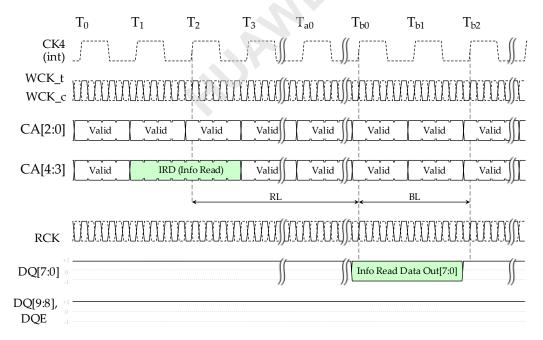

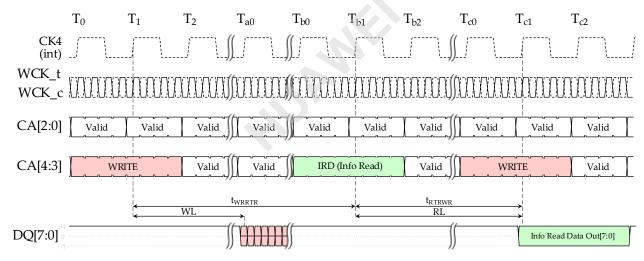

| Figure 62 – | - Info Read Operation                                                              | 128 |

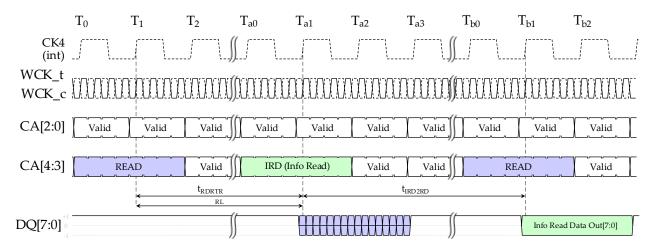

| Figure 63 – | - Example of Info Read Operation Between Consecutive Reads                         | 132 |

| Figure 64 – | - Example of Info Read Operation Between Consecutive Writes                        | 132 |

| Figure 65 – | - Activate Command                                                                 | 136 |

| Figure 66 – | - Row Activation Command Cycle                                                     | 137 |

| Figure 67 – | - Write Command                                                                    | 138 |

| Figure 68 – | - Write Lane Timings                                                               | 141 |

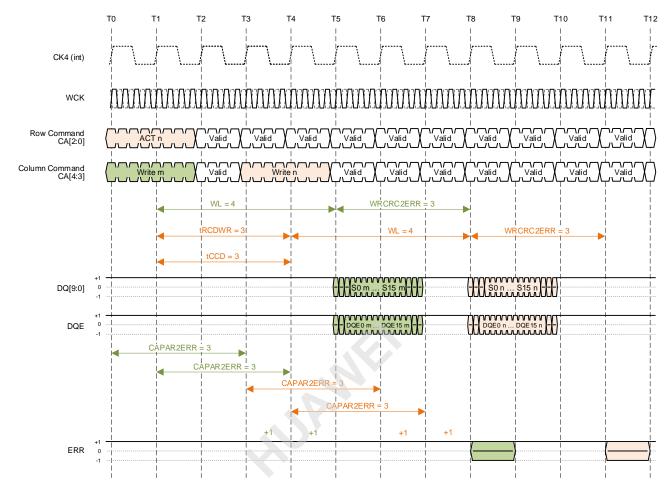

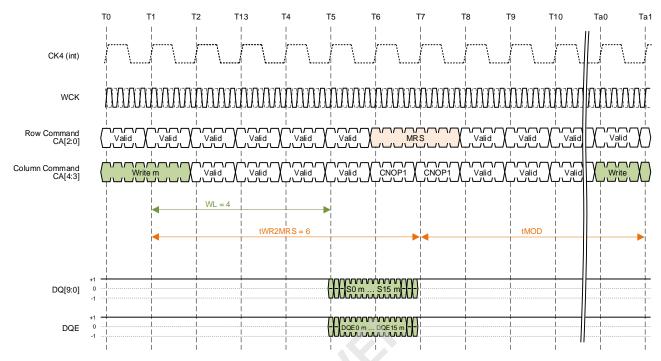

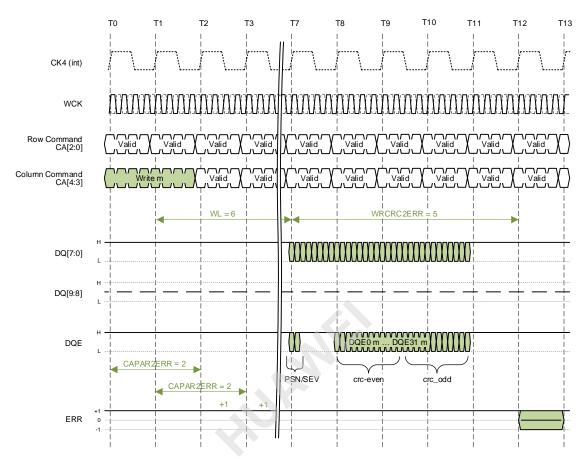

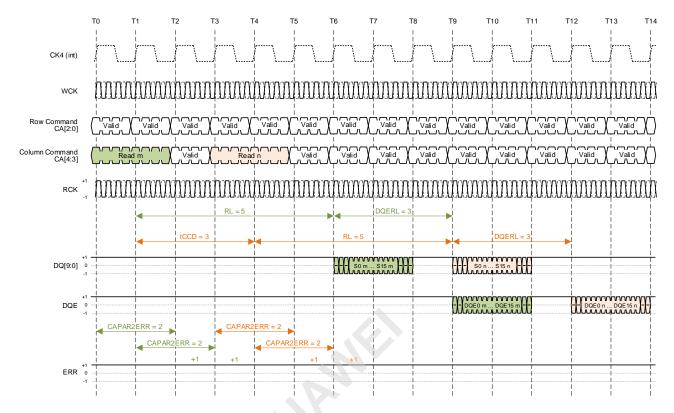

| Figure 69 – | - Single PAM3 Write with WRCRC and CA Parity Enabled                               | 142 |

| Figure 70 – | - Single PAM3 Write with WRCRC Disabled                                            | 143 |

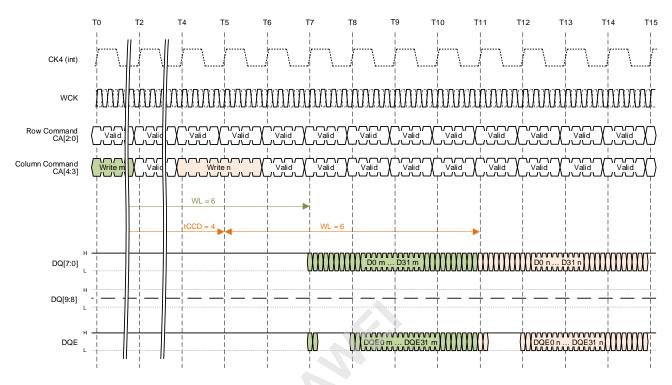

| Figure 71 – | - Gapless PAM3 Writes, Different Banks (tCCD = 2)                                  | 144 |

| Figure 72 – | - Non-Gapless PAM3 Writes, Different Banks (tCCD = 3)                              | 145 |

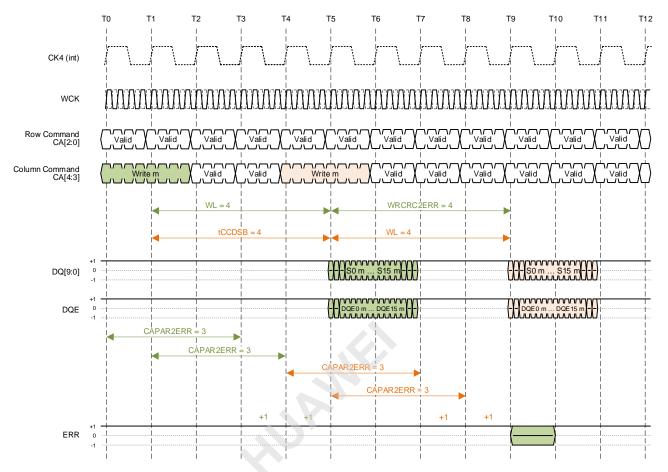

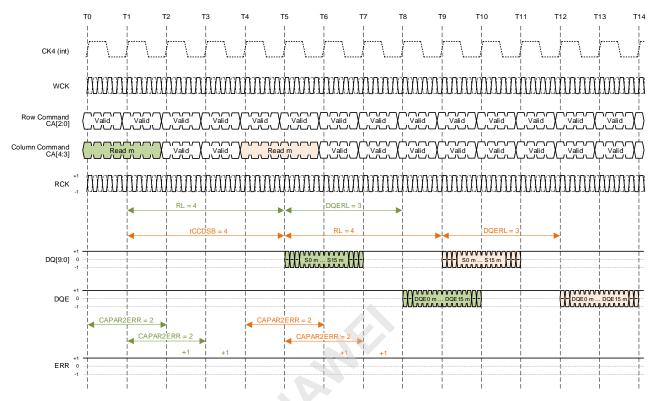

| Figure 73 – | - Non-Gapless PAM3 Writes, Same Bank (tCCDSB = 4)                                  | 146 |

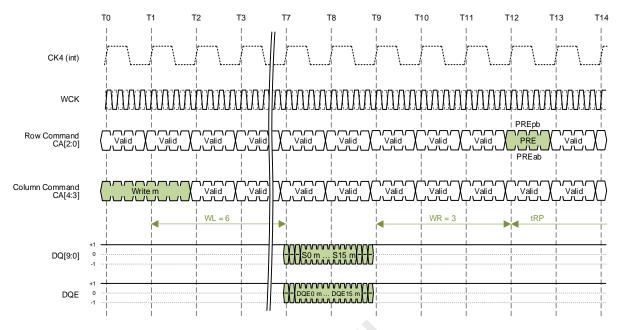

| Figure 74 – | - Write to Precharge (PAM3 Mode)                                                   | 147 |

| Figure 75 – | - Write to Read (PAM3 Mode)                                                        | 148 |

| Figure 76 – | - Write to MRS (PAM3 Mode)                                                         | 149 |

| Figure 77 – | - Single NRZ Write with WRCRC and CA Parity Enabled                                | 150 |

| Figure 78 – | - Gapless NRZ Writes (tCCD = 4)                                                    | 151 |

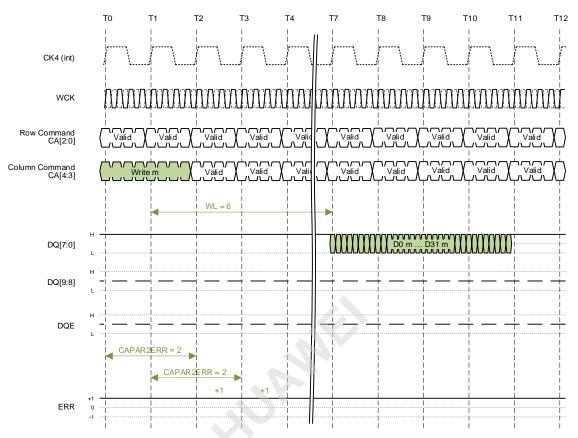

| Figure 79 – | - Single NRZ Write with DQE Disabled (RDCRC, WRCRC, Severity, and Poison Disabled) | 152 |

| Figure 80 – | RCK Always On Enable/Disable Timings                                               | 154 |

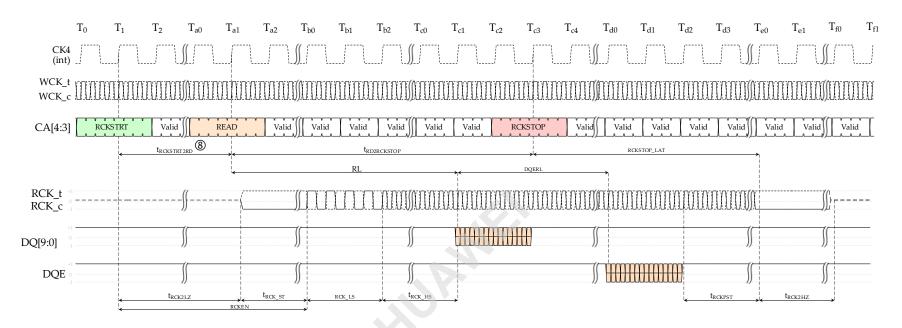

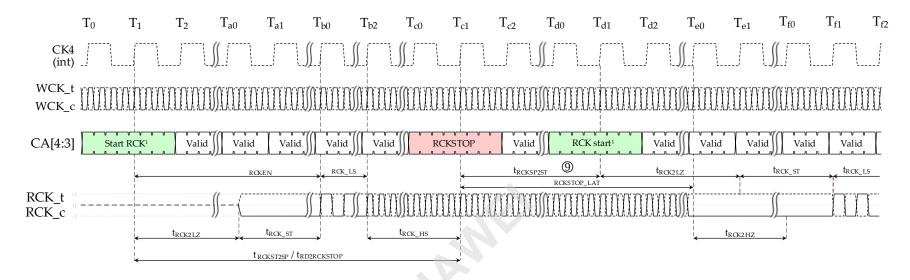

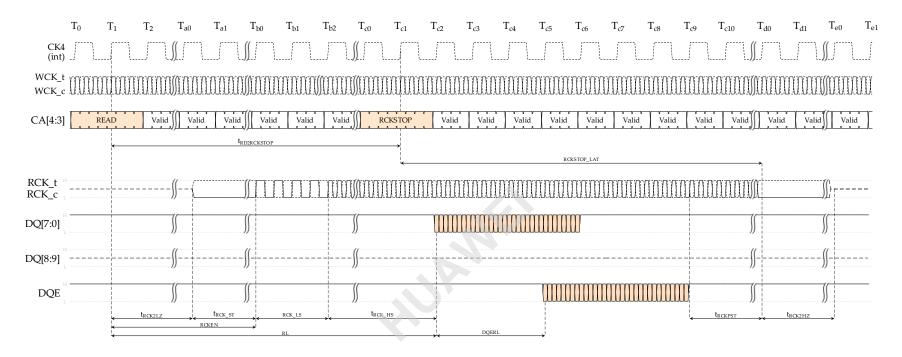

| Figure 81 – | RCKSTRT and RCKSTOP Commands                                                       | 155 |

| Figure 82 – | - Overview of the RCK Start/Stop Protocol                                          | 157 |

| Figure 83 – | - Example of RCK Triggered with READ Command                                       | 159 |

| Figure 84 – | Example of RCK Triggered with RCKSTRT Command Followed by a READ Command           | 160 |

| Figure 85 – | RCKSTOP Command Followed by RCK Start Command                                      | 161 |

| Figure 86 – | - Example of RCK Triggered by READ Command in NRZ Mode                             | 162 |

| Figure 87 – | - Read Command                                                                     | 163 |

| Figure 88 – | - Read Lane Timings                                                                | 166 |

| Figure 89 — Single PAM3 Read with RDCRC and CA Parity Enabled                                     | 167 |

|---------------------------------------------------------------------------------------------------|-----|

| Figure 90 — Single PAM3 Read with RDCRC Disabled                                                  | 168 |

| Figure 91 — Gapless PAM3 Reads, Different Banks (tCCD = 2)                                        | 169 |

| Figure 92 — Non-Gapless PAM3 Reads, Different Banks (tCCD = 3)                                    | 170 |

| Figure 93 — Non-Gapless PAM3 Reads, Same Bank (tCCDSB = 4)                                        | 171 |

| Figure 94 — Read to Precharge (PAM3 Mode)                                                         | 172 |

| Figure 95 — Read to Write (PAM3 Mode)                                                             | 173 |

| Figure 96 — Read to MRS (PAM3 Mode)                                                               | 174 |

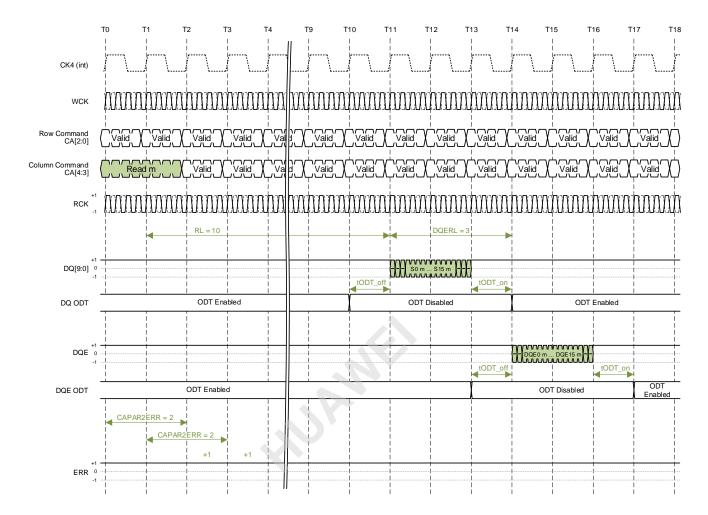

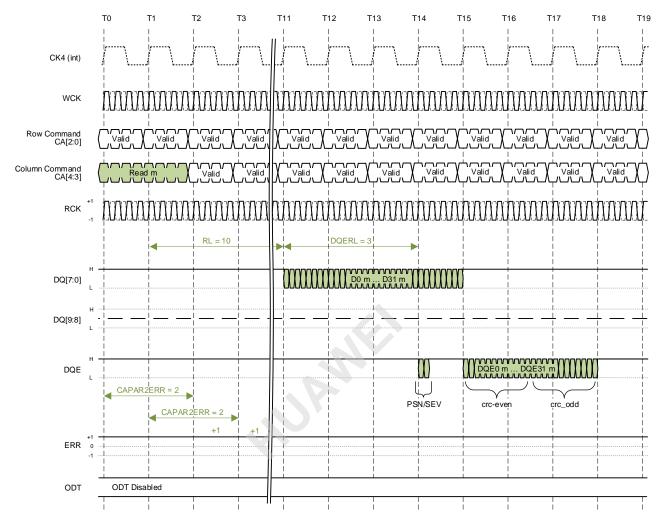

| Figure 97 — Single NRZ Read with RDCRC and CA Parity Enabled, ODT Disabled                        | 175 |

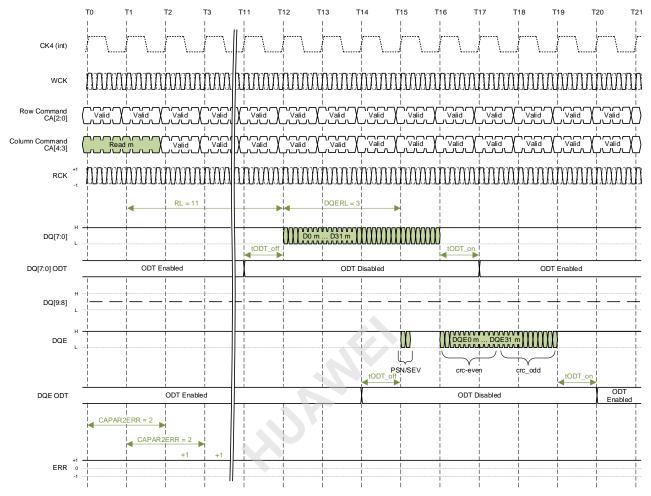

| Figure 98 — Single NRZ Read with RDCRC, CA Parity and ODT Enabled                                 | 176 |

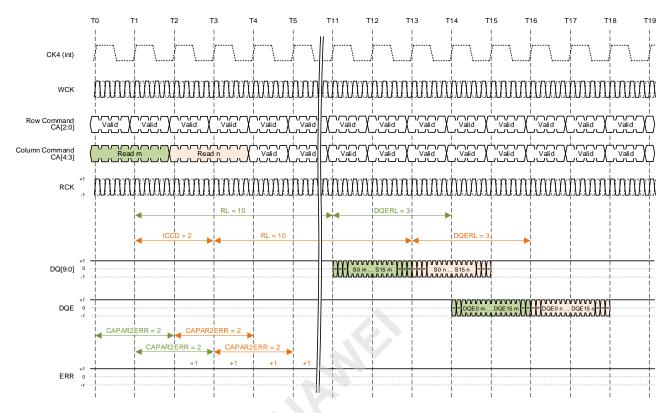

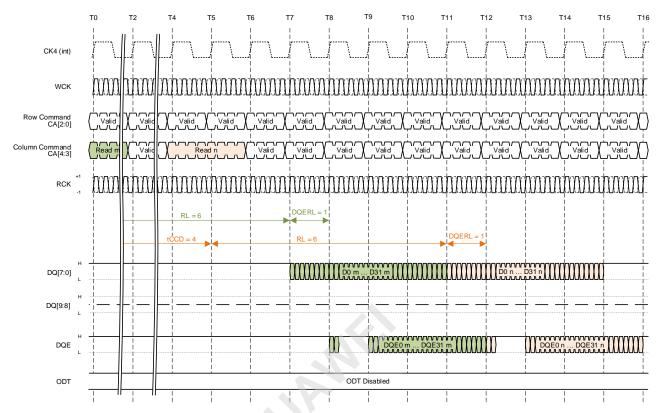

| Figure 99 — Gapless NRZ Reads (tCCD = 4)                                                          | 177 |

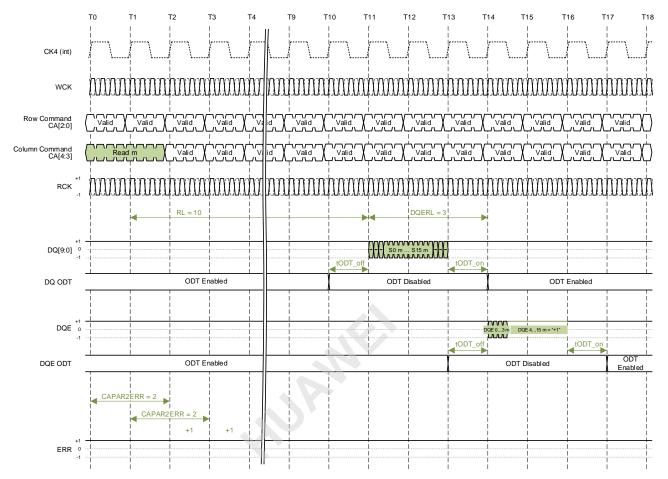

| Figure 100 — Single NRZ Read with DQE Disabled (RDCRC, WRCRC, Severity, and Poison Disabled)      | 178 |

| Figure 101 — Single NRZ Read with DQE Disabled and SEV2ERR Enabled                                | 179 |

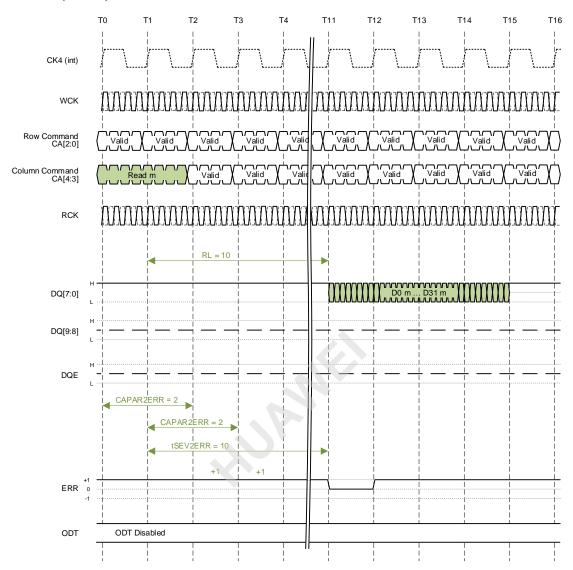

| Figure 102 — Precharge Commands                                                                   | 180 |

| Figure 103 — Refresh All-Bank (REFab) and Refresh Per-Bank (REFpb) Commands                       | 182 |

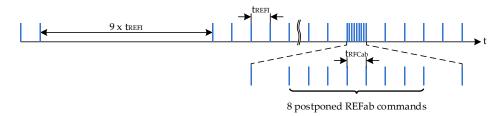

| Figure 104 — Postponing Refresh All-Bank Commands (Example)                                       | 183 |

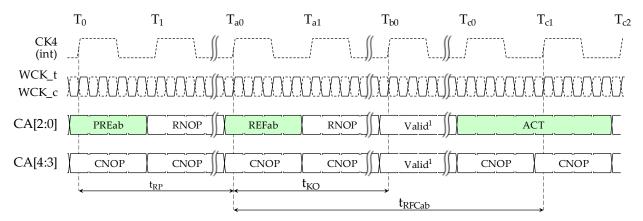

| Figure 105 — REFab Timings                                                                        | 184 |

| Figure 106 — REFpb Timings                                                                        | 185 |

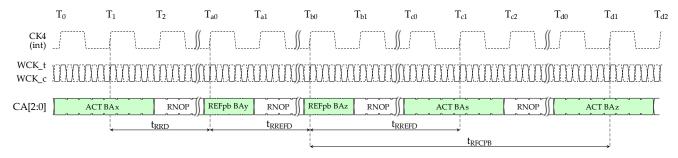

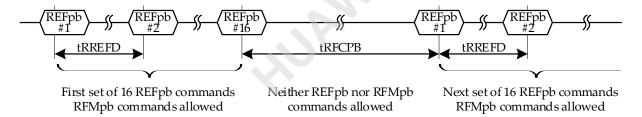

| Figure 107 — Sets of REFpb Commands                                                               | 185 |

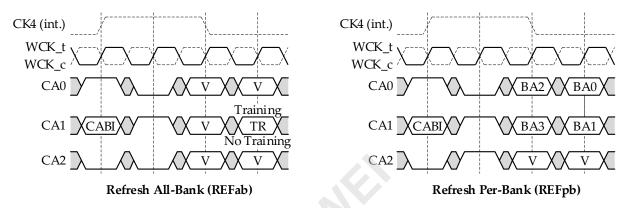

| Figure 108 — Refresh Management All-Bank (RFMab) and Refresh Management Per-Bank (RFMpb) Commands | 189 |

| Figure 109 — Self Refresh Entry and Exit Commands                                                 | 195 |

| Figure 110 — Self Refresh Entry and Exit                                                          | 196 |

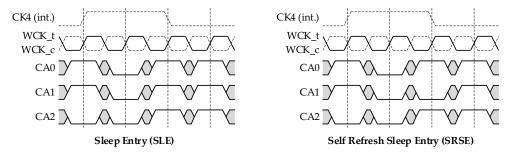

| Figure 111 — Sleep Mode Entry Commands                                                            | 199 |

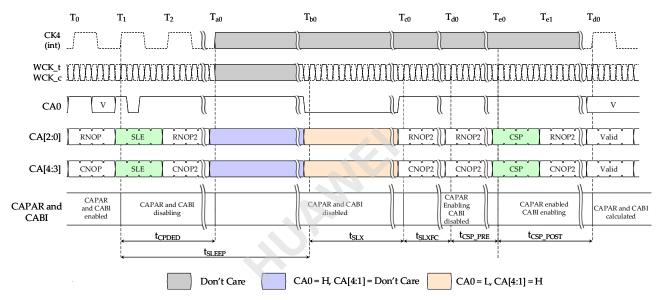

| Figure 112 — Sleep Mode Entry and Exit                                                            | 200 |

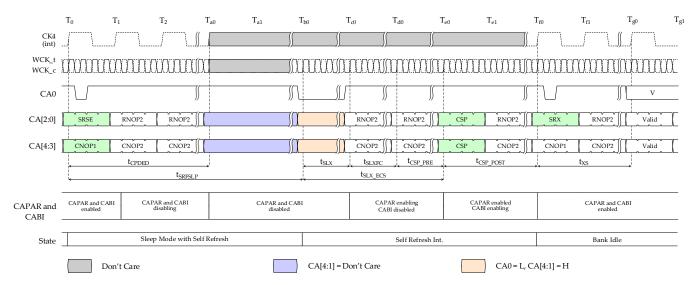

| Figure 113 — Self Refresh Sleep Mode Entry and Exit                                               | 201 |

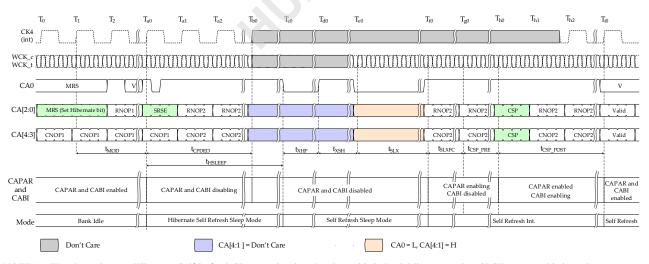

| Figure 114 — Hibernate Self Refresh Sleep Mode Entry and Exit                                     | 202 |

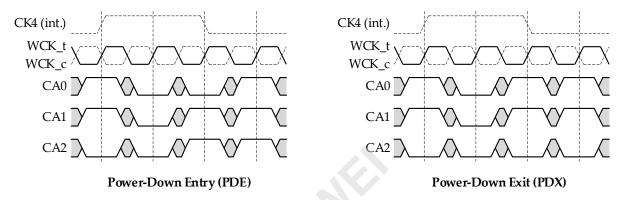

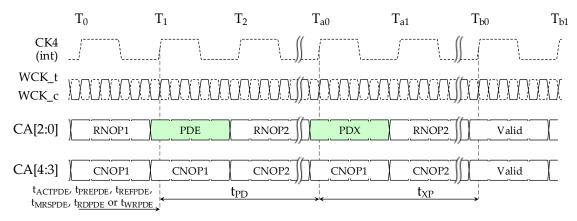

| Figure 115 — Power-Down Entry and Exit Commands                                                   | 203 |

| Figure 116 — Power-Down Entry and Exit                                                            | 204 |

| Figure 117 — Example of WCK Frequency Change                                                      | 206 |

| Figure 118 — Example of Dynamic Voltage Change                                                    | 208 |

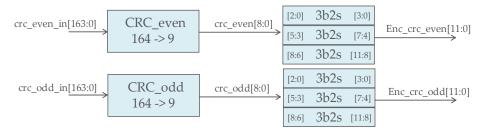

| Figure 119 — CRC-9 Even and Odd Blocks and Output Encoding                                        | 210 |

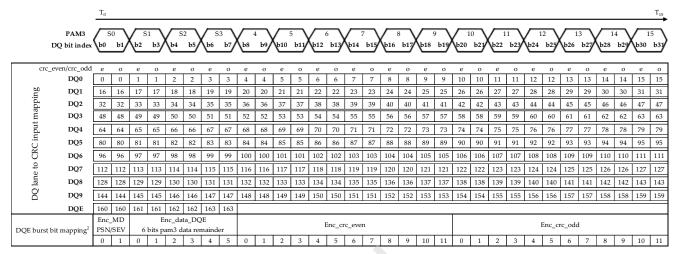

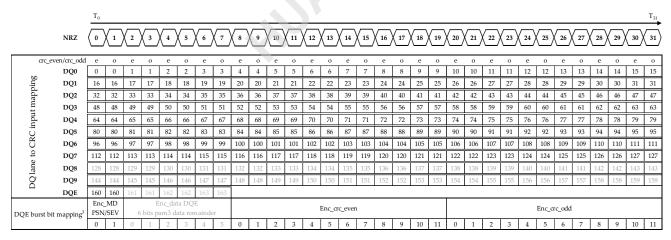

| Figure 120 — DO to CRC Input/Output Bit Assignation and DOE Burst Bit Order in PAM3               | 211 |

| Figure 121 — DQ to CRC Input Bit Assignation and DQE Burst Bit Order in NRZ                                 | .211  |

|-------------------------------------------------------------------------------------------------------------|-------|

| Figure 122 — RTL Implementation of the CRC Calculation Based on the Given CRC-9 Polynomial                  | .212  |

| Figure 123 — RTL Implementation of the CRC Input and Output Bit Assignments                                 | .213  |

| Figure 124 — On-die ECC Overview Diagram Example                                                            | .214  |

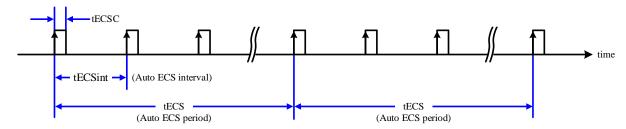

| Figure 125 — ECS Operation Timing                                                                           | .218  |

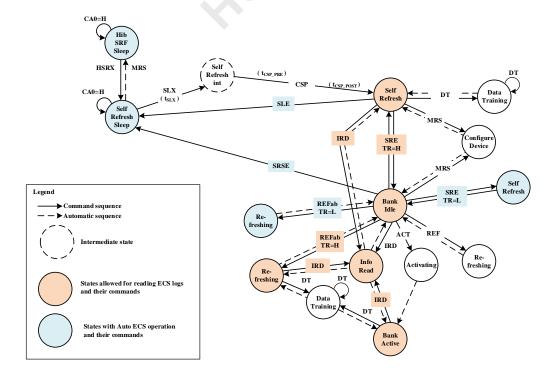

| Figure 126 — Auto ECS and ECS Log Read Out State Diagram                                                    | . 221 |

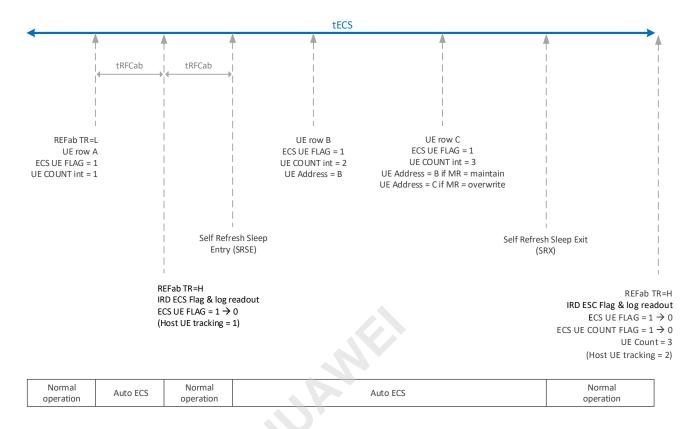

| Figure 127 — Example ECS Operation – UEAL and UECL                                                          | . 222 |

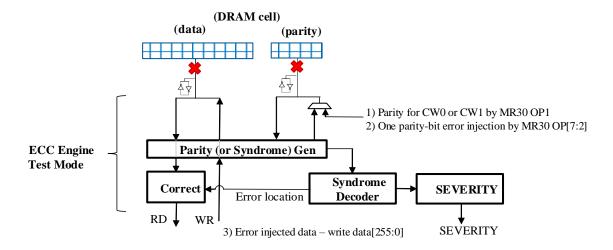

| Figure 128 — Example of the Block Diagram of On-die ECC Engine and Path for ECC Engine Test Mode            | . 225 |

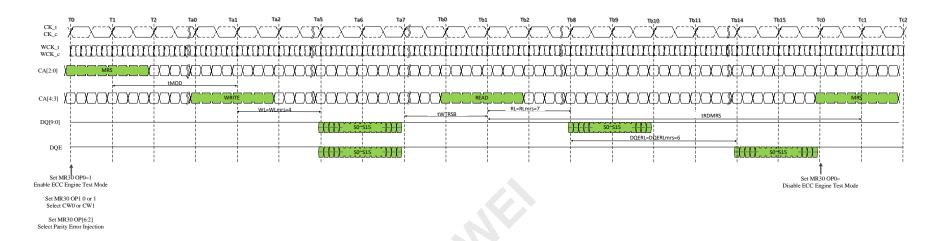

| Figure 129 — Timing Diagram of ECC Engine Test Mode                                                         | . 227 |

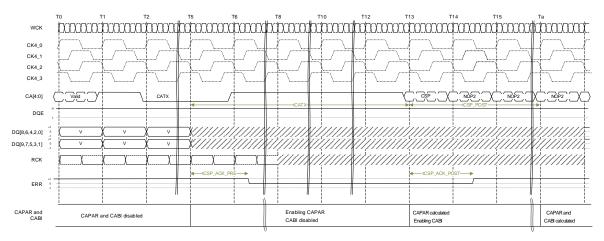

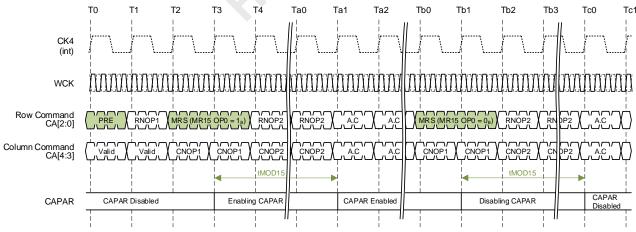

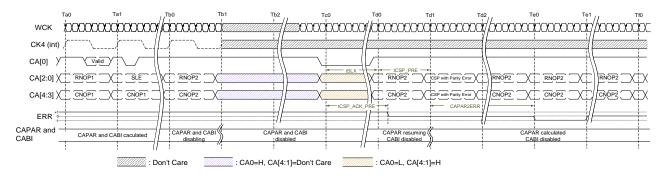

| Figure 130 — Enabling and Disabling Command Address Parity (CAPAR) with FD_FLAG = $1_B$                     | . 228 |

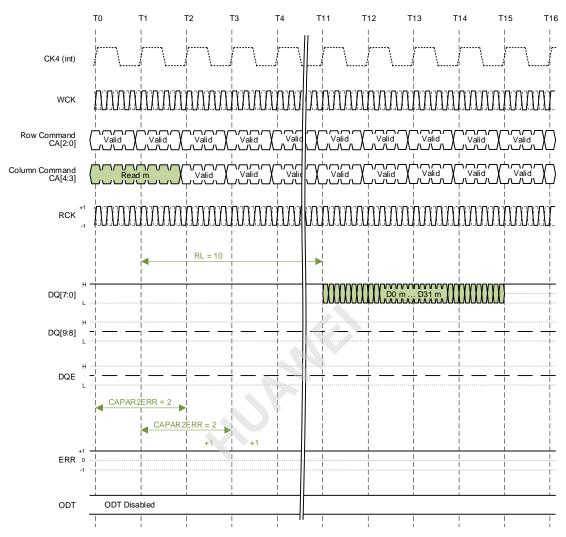

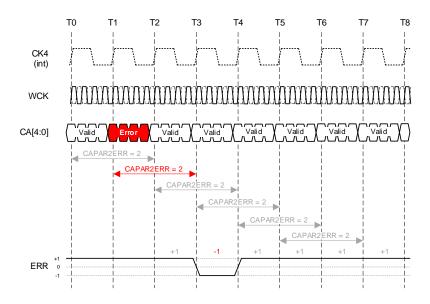

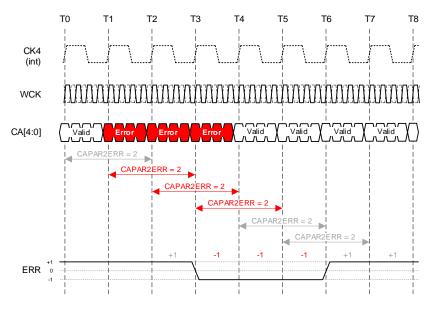

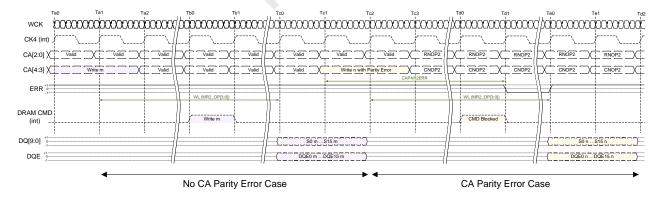

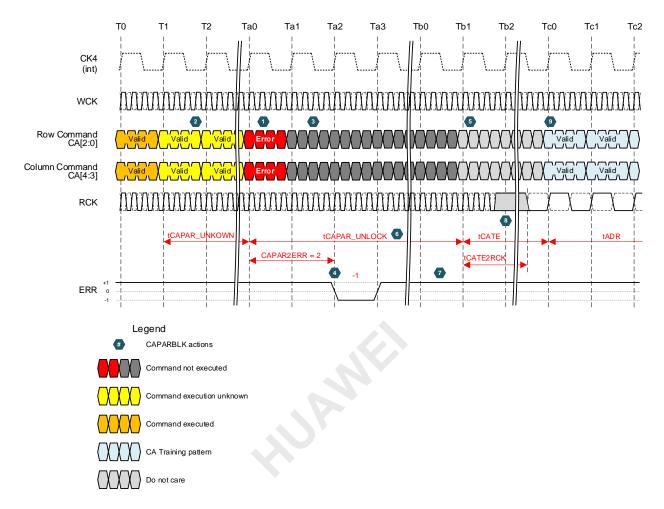

| Figure 131 — Single Command Address Parity Error with Command Blocking Disabled                             | . 229 |

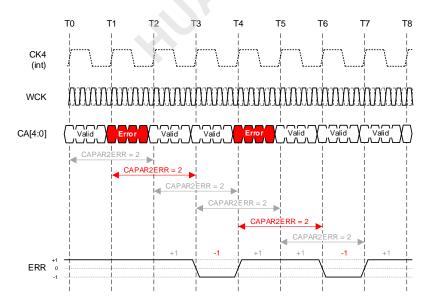

| Figure 132 — Multiple Command Address Parity Errors with Command Blocking Disabled                          | . 229 |

| Figure 133 — Persistent Command Address Parity Errors with Command Blocking Disabled                        | . 230 |

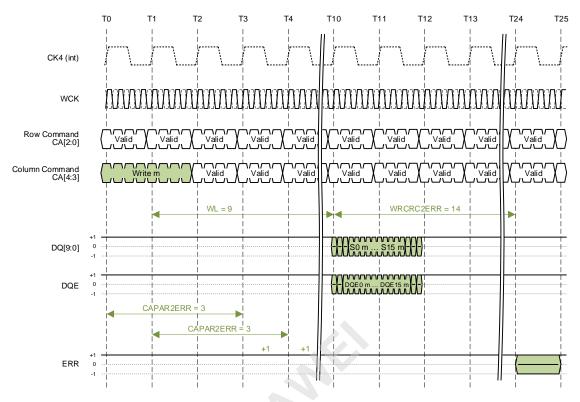

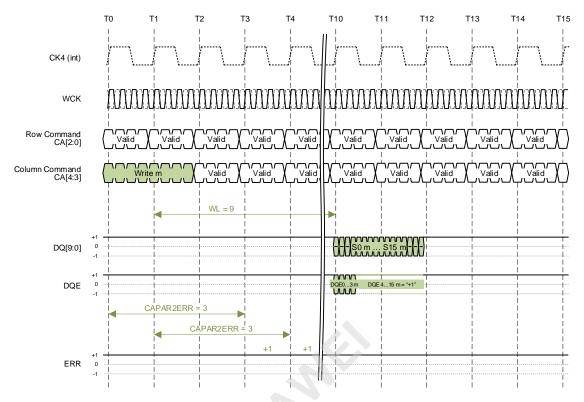

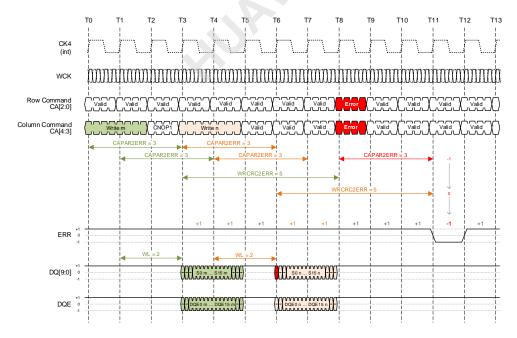

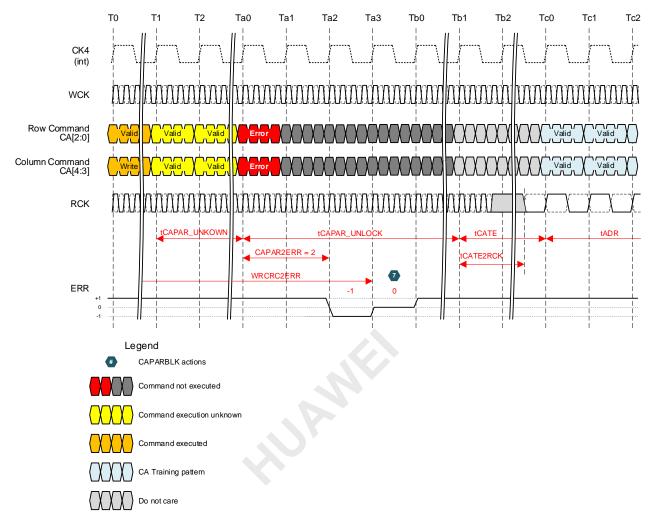

| Figure 134 — WRCRC and CAPAR ERR Signaling (Same Cycle)                                                     | . 230 |

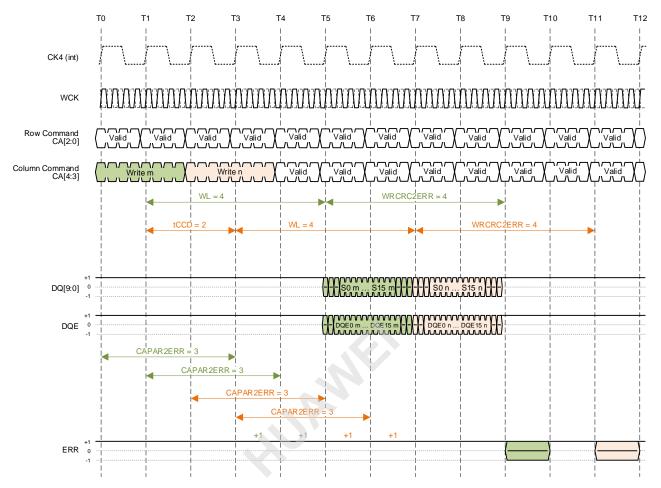

| Figure 135 — WRCRC and CAPAR ERR Signaling (WRCRC before CAPAR)                                             | . 231 |

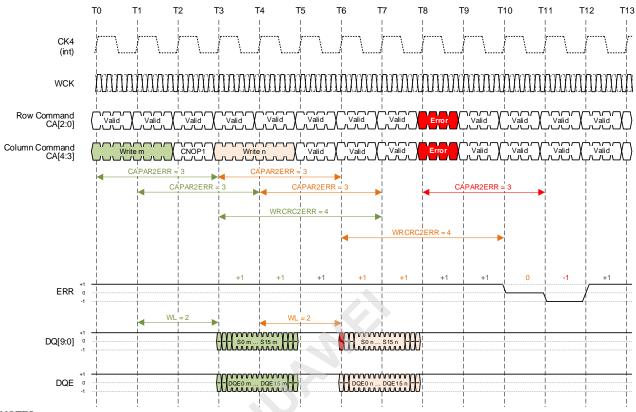

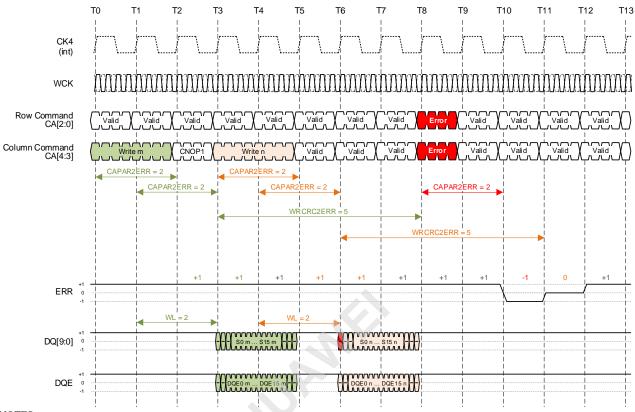

| Figure 136 — WRCRC and CAPAR ERR Signaling (CAPAR before WRCRC)                                             | . 232 |

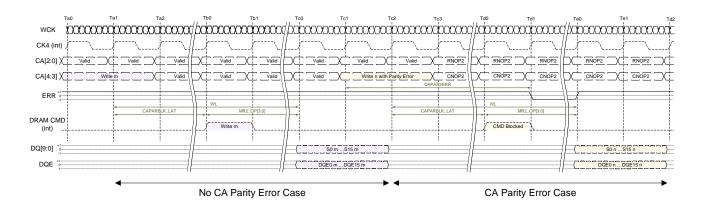

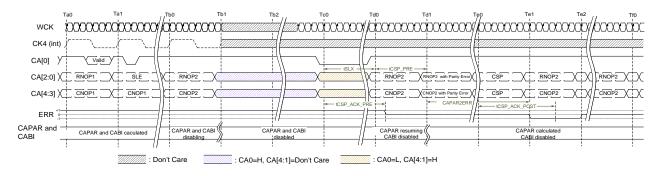

| Figure 137 — Implicit CAPARBLK_LAT                                                                          | . 233 |

| Figure 138 — Explicit CAPARBLK_LAT                                                                          | . 234 |

| Figure 139 — Enabling and Disabling Command Address Parity Command Blocking (CAPARBLK) with FD_FLAG = $1_B$ | .236  |

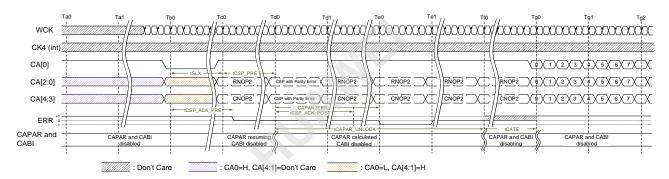

| Figure 140 — Command Blocking                                                                               | . 237 |

| Figure 141 — Command Blocking (WRCRC Error after CAPAR Error)                                               | . 238 |

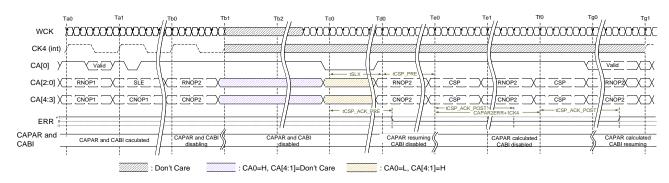

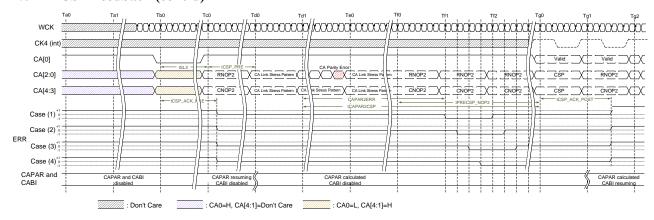

| Figure 142 — CA Training Exit without CSP Error.                                                            | . 239 |

| Figure 143 — Sleep Mode Entry and Exit without CSP Error                                                    | . 239 |

| Figure 144 — Sleep Mode Entry and Exit with CSP Parity Error                                                | . 240 |

| Figure 145 — Sleep Mode Entry and Exit with CSP Parity Error within 1CK4 before CSP Command                 | . 240 |

| Figure 146 — Sleep Mode Entry and Exit with CSP Retry Pass.                                                 | . 241 |

| Figure 147 — Sleep Mode Exit with CSP Command with Parity Error when CAPARBLK is Enabled                    | . 241 |

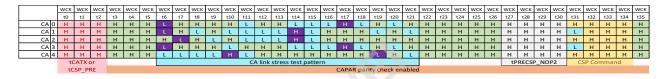

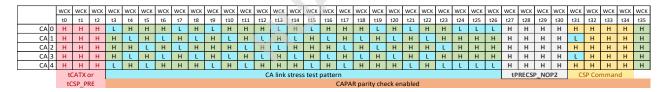

| Figure 148 — Sleep Mode Exit with CA Link Stress Pattern                                                    | . 244 |

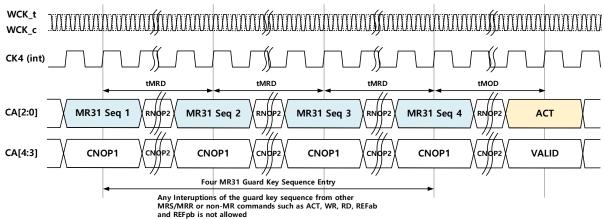

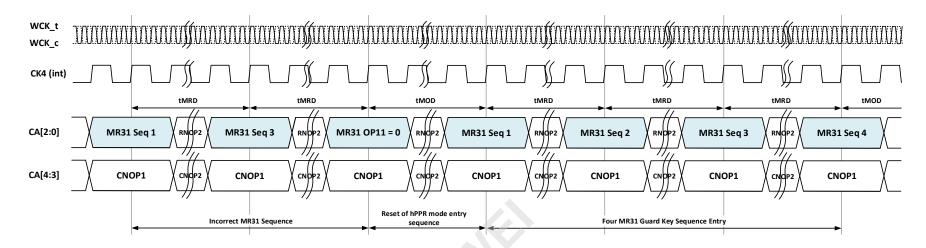

| Figure 149 — Guard Key Timing Diagram                                                                       | . 246 |

| Figure 150 — Incorrect Guard Key Sequence and hPPR Mode Reset                                               | . 247 |

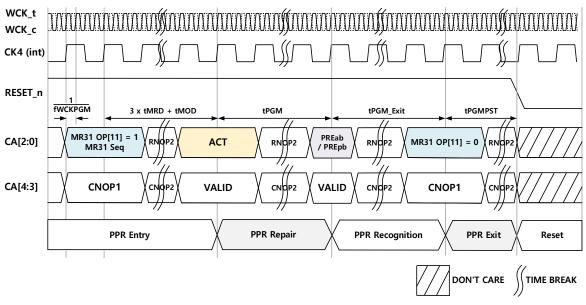

| Figure 151 — hPPR Fail Row Repair Timing                                                                    | . 249 |

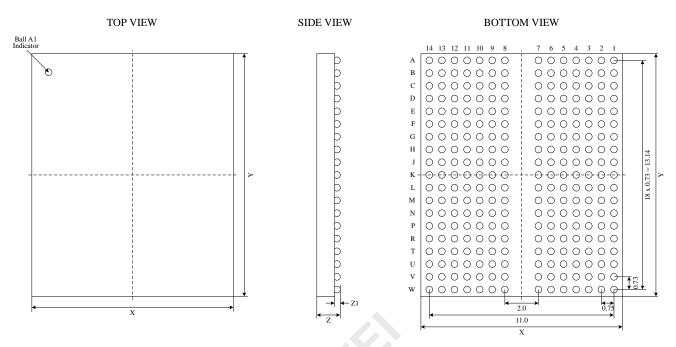

| Figure 152 — 266 Ball BGA Ball-Out                                                                          | .292  |

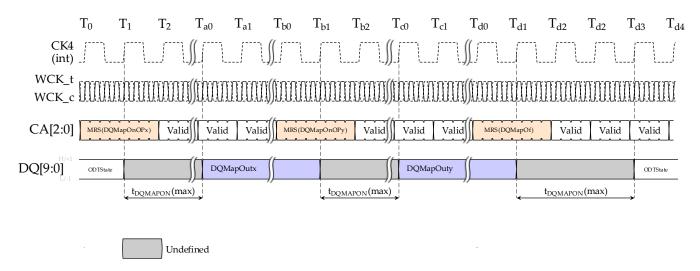

| Figure 153 — DQ Map Mode Timing                                        | 295   |

|------------------------------------------------------------------------|-------|

| Figure 154 — Package Dimensions                                        | 296   |

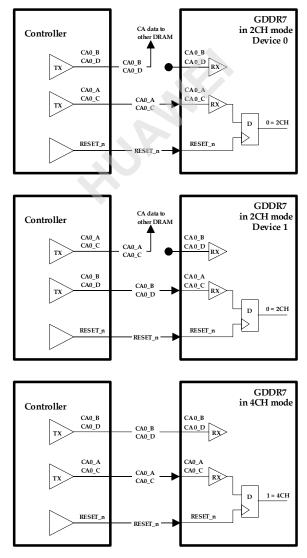

| Figure 155 — Enabling 2-Channel Mode                                   | 297   |

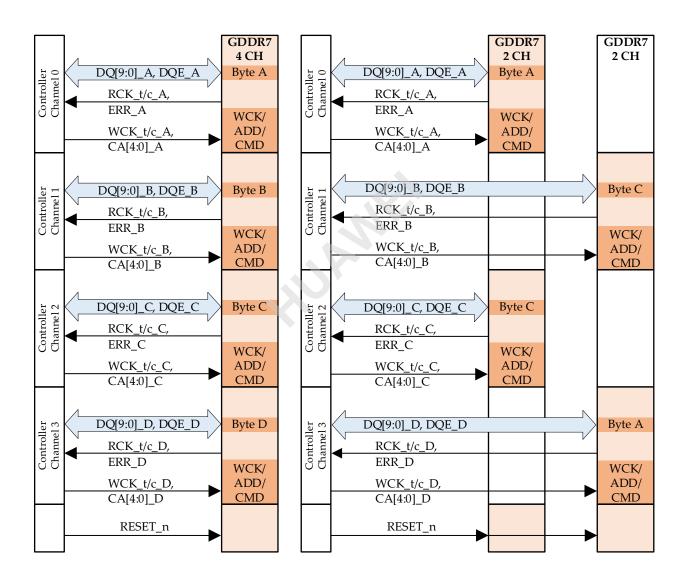

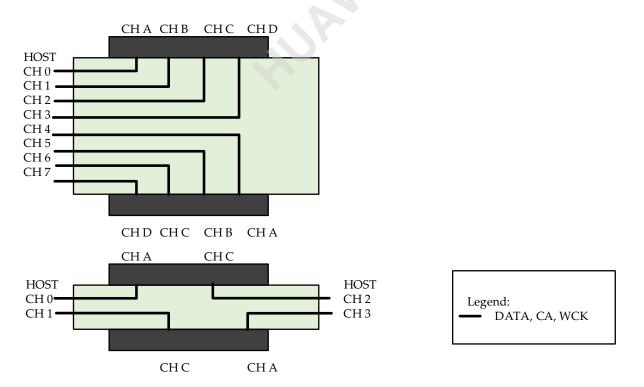

| Figure 156 — Example System View for 4-Channel Mode vs. 2-Channel Mode | 298   |

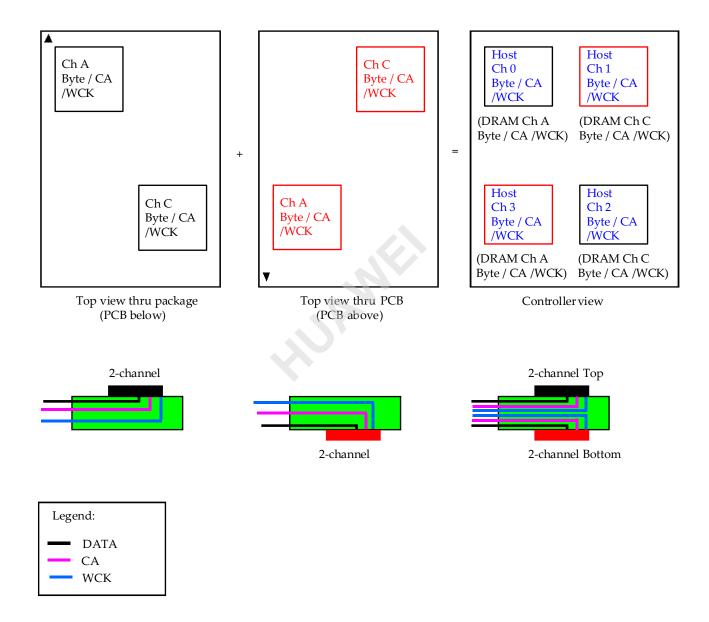

| Figure 157 — Byte Orientation in Clamshell Topology                    | 299   |

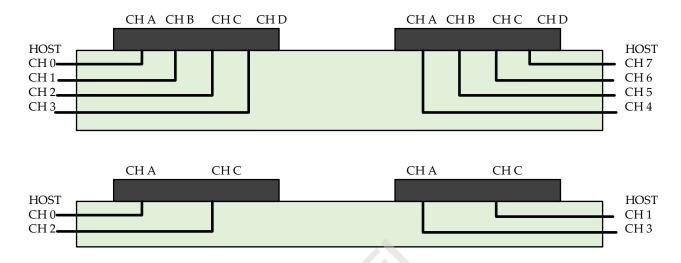

| Figure 158 — Example GDDR7 PCB Layout Topologies                       |       |

| List of Tables                                                         |       |

|                                                                        | Pages |

| Table 1 — Example of WCK and Interface Signal Frequency Relationship   |       |

| Table 2 — Addressing Scheme                                            |       |

| Table 3 — Example of CAPAR (Even Parity)                               |       |

| Table 4 — PAM3 Signal Levels                                           |       |

| Table 5 — 3b2S Encoder for CRC, Data Remainder, and LFSR Training      |       |

| Table 6 — Severity and Poison 2b1S Encoder/Decoder                     |       |

| Table 7 — 11b7S Encoder/Decoder Table                                  |       |

| Table 8 — 5b3S Encoder/Decoder Table                                   |       |

| Table 9 — Check Bit Truth Table (b_p)                                  |       |

| Table 10 — 7b4S Encoding/Decoding Table                                |       |

| Table 11 — ERR PAM3 Encoding (PAM3 and NRZ Mode)                       |       |

| Table 12 — ERR PAM3 Encoding (Optional SEV2ERR Mode)                   |       |

| Table 13 — Features using ERR and the ERR Signal State                 |       |

| Table 14 — State Diagram Command Codes                                 |       |

| Table 15 — Device Initialization Timings                               |       |

| Table 16 — WCK Termination                                             |       |

| Table 17 — CA Termination                                              |       |

| Table 18 — 4CH / 2CH Mode                                              |       |

| Table 19 — Mode Register Overview                                      |       |

| Table 20 — Mode Register 0 (MR0)                                       |       |

| Table 21 — Mode Register 1 (MR1)                                       |       |

| Table 22 — Mode Register 2 (MR2)                                       |       |

| Table 23 — Mode Register 3 (MR3)                                       |       |

| Table 24 — Mode Register 4 (MR4)                                       |       |

| Table 25 — Mode Register 5 (MR5)                                       |       |

| Table 26 — Mode Registers 6 (MR6)                                      |       |

| Table 27 — Mode Registers 7 (MR7)                                      | 47    |

| Table 28 — Mode Register 8 (MR8)                                                  |    |

|-----------------------------------------------------------------------------------|----|

| Table 29 — Mode Register 9 (MR9)                                                  |    |

| Table 30 — Mode Register 10 (MR10)                                                |    |

| Table 31 — Mode Register 11 (MR11)                                                | 50 |

| Table 32 — Mode Register 12 (MR12)                                                | 51 |

| Table 33 — Mode Register 13 (MR13)                                                | 52 |

| Table 34 — Mode Register 14 (MR14)                                                | 53 |

| Table 35 — VREFCA Level ( $V_{DDQ} = 1.20 \text{ V}$ )                            | 53 |

| Table 36 — Mode Register 15 (MR15)                                                | 55 |

| Table 37 — Mode Registers 16 (MR16)                                               |    |

| Table 38 — Mode Registers 17 (MR17)                                               | 57 |

| Table 39 — VREFDL, VREFDH, and VREFD2 Levels (V <sub>DDQ</sub> = 1.20 V)          | 58 |

| Table 40 — Mode Registers 18 (MR18)                                               | 61 |

| Table 41 — Mode Registers 19 (MR19)                                               | 62 |

| Table 42 — Mode Register 20 (MR20)                                                |    |

| Table 43 — Mode Register 21 (MR21)                                                |    |

| Table 44 — Mode Register 22 (MR22)                                                | 64 |

| Table 45 — Mode Register 23 (MR23)                                                | 65 |

| Table 46 — Mode Registers 24 (MR24)                                               | 66 |

| Table 47 — Mode Registers 25 (MR25)                                               | 66 |

| Table 48 — Mode Register 26 (MR26)                                                | 67 |

| Table 49 — Mode Register 27 (MR27)                                                | 68 |

| Table 50 — Mode Register 28 (MR28)                                                | 68 |

| Table 51 — Mode Register 29 (MR29)                                                | 69 |

| Table 52 — Mode Register 30 (MR30)                                                | 69 |

| Table 53 — Mode Register 31 (MR31)                                                | 70 |

| Table 54 — Mode Register Default Settings                                         | 70 |

| Table 55 — CA Capture to DQ Return Mapping                                        | 74 |

| Table 56 — AC Timings in Command Address Training Mode                            | 78 |

| Table 57 — Data Training Eye Mask                                                 | 82 |

| Table 58 — Data Training AC Timings                                               | 83 |

| Table 59 — Encoder for CRC, Data Remainder, and LFSR Training                     | 86 |

| Table 60 — LFSR Pattern Inversion and Pattern Masking                             | 88 |

| Table 61 — Example LFSR PRBS15 Pattern Generator Output (before 3b2S Encoder)     | 90 |

| Table 62 — Example WRTR Output Burt Stream for DQ[9] (DQ Group 2), where          |    |

| LFSR_SHIFT_SEL = $0x0$ , LFSR_INV = $0x0$ , DT_MASK = $0x0$                       | 91 |

| Table 63 — Example WRTR Output Burst Stream for Single Burst from DQE and DQ[9:0] | 91 |

| Table 64 — Binary to PAM3 Symbol Mapping                                          | 99 |

| Table 65 — Burst Error Counter Data Encoding                                | 109 |

|-----------------------------------------------------------------------------|-----|

| Table 66 — WCK Oscillator Matching Error Specification                      | 113 |

| Table 67 — tWCK2CA Offset Due to Temperature and Voltage Variation          | 114 |

| Table 68 — CAOSC Mode Register                                              | 114 |

| Table 69 — Info Read Data                                                   | 114 |

| Table 70 — CAOSC (WCK2CA) Interval Oscillator AC Timing                     | 115 |

| Table 71 — DCC Timing                                                       | 116 |

| Table 72 — DCC Control Signals                                              | 116 |

| Table 73 — CABI and CAPAR Bit Positions                                     | 117 |

| Table 74 — Truth Table – Commands                                           | 118 |

| Table 75 — Info Read Data                                                   | 129 |

| Table 76 — Info Read Timings <sup>1</sup>                                   | 131 |

| Table 77 — Info Register Address 0 – Vendor ID1                             | 132 |

| Table 78 — Info Register Address 1 – Vendor ID2                             | 133 |

| Table 79 — Info Register Address 2 – Vendor ID3                             | 133 |

| Table 80 — Info Register Address 3 – Vendor ID4                             | 134 |

| Table 81 — Info Register Address 16 – Temperature Sensor and ECS Error Flag | 134 |

| Table 82 — Info Register Address 17 – Maximum Temperature Log               | 135 |

| Table 83 — Info Register Addresses 25 and 26 – hPPR Resources               | 135 |

| Table 84 — Info Register Addresses 32 to 39 – Serial ID                     | 135 |

| Table 85 — RCK Related AC Timings                                           | 158 |

| Table 86 — DQE State (NRZ Mode)                                             | 164 |

| Table 87 — Auto Precharge Enabled/Disabled and PREab / PREpb Timings        | 181 |

| Table 88 — Refresh Counter Increments with REFpb                            | 186 |

| Table 89 — REFab and REFpb Command Scheduling Requirements                  | 187 |

| Table 90 — RFM Support Definition in Info Read Register 4                   | 188 |

| Table 91 — RAAIMT Definition in Info Read Register 4                        | 188 |

| Table 92 — RAAMMT Definition in Info Read Register 4                        | 189 |

| Table 93 — RAADEC Definition in Info Read Register 4                        | 190 |

| Table 94 — ARFM Support Definition in Info Read Register 4                  | 191 |

| Table 95 — Mode Register Definition for Adaptive RFM Levels                 | 191 |

| Table 96 — RFM Commands Perceived by GDDR7 SGRAM                            | 192 |

| Table 97 — ARFM Level Definition in Info Read Registers 5 to 7              | 192 |

| Table 98 — Bounded Refresh Configuration and tDRFM Timings                  | 194 |

| Table 99 — Commands Supported during Self Refresh                           | 196 |

| Table 100 — Signal States During Self Refresh                               | 197 |

| Table 101 — Signal States During Sleep Modes                                | 201 |

| Table 102 — | Signal States During Power-Down                                                                              | 204 |

|-------------|--------------------------------------------------------------------------------------------------------------|-----|

| Table 103 — | Data Integrity Related Features                                                                              | 209 |

| Table 104 — | GDDR7 CRC Error Detection Details                                                                            | 210 |

| Table 105 — | Transparency Attributes and their Access/Control Mechanism                                                   | 216 |

| Table 106 — | DQE Severity/Poison (SEV/PSN) Bit Truth Table                                                                | 216 |

| Table 107 — | ECS Mode Registers                                                                                           | 217 |

| Table 108 — | tECSint per Channel                                                                                          | 218 |

| Table 109 — | ECS Error Types                                                                                              | 219 |

| Table 110 — | ECC Engine Test Modes                                                                                        | 223 |

| Table 111 — | Severity Report According to IRA 2 DQ 2 (ECC_ENG_CE) Status                                                  | 223 |

| Table 112 — | Example of Error Vectors, Parity Bit Error Injection and Corresponding Severity IRA 2 $DQ2 = 1_B$            | 225 |

| Table 113 — | Example of Error Vectors, Parity Bit Error Injection and Corresponding Severity IRA 2 DQ2 = $0_B$ (Optional) | 226 |

| Table 114 — | Command Blocking Impacted AC Timings                                                                         | 234 |

| Table 115 — | tCAPAR_UNLOCK                                                                                                | 235 |

| Table 116 — | CSP Feedback Support Definition in Info Read Address 3                                                       | 241 |

| Table 117 — | Mode Register Definition for CSP Feedback                                                                    | 242 |

| Table 118 — | ERR Pin Status after CSP                                                                                     | 242 |

| Table 119 — | Reference Example of CA Link Stress Test Pattern                                                             | 243 |

| Table 120 — | Intentional Parity Error Pattern                                                                             | 244 |

| Table 121 — | AC Parameters in CSP Feedback                                                                                | 245 |

| Table 122 — | Guard Key Encoding for MR31                                                                                  | 248 |

| Table 123 — | Mode Register Bits for hPPR                                                                                  | 249 |

| Table 124 — | hPPR Timing Parameters                                                                                       | 249 |

| Table 125 — | Absolute Maximum Ratings                                                                                     | 250 |

| Table 126 — | Silicon Pad Capacitance                                                                                      | 250 |

| Table 127 — | Package Electrical Specification                                                                             | 251 |

| Table 128 — | Package Thermal Characteristics                                                                              | 251 |

| Table 129 — | Electrostatic Discharge Sensitivity Characteristics                                                          | 252 |

| Table 130 — | Operating Temperature Range Example 1                                                                        | 252 |

| Table 131 — | Operating Temperature Range Example 2                                                                        | 252 |

| Table 132 — | Operating Temperature Range Example 3                                                                        | 252 |

| Table 133 — | DC Operating Conditions                                                                                      | 254 |

| Table 134 — | IDD Specifications and Test Conditions                                                                       | 258 |

| Table 135 — | AC Parameter Condition for IDD Test                                                                          | 261 |

| Table 136 — | IDD0 Measurement-Loop Pattern                                                                                | 261 |

| Table 137   | IDD0F Measurement I oon Pattern                                                                              | 262 |

| Table 138 — IDD4R Measurement-Loop Pattern                                              | . 263 |

|-----------------------------------------------------------------------------------------|-------|

| Sable 139 — IDD4W Measurement-Loop Pattern                                              | . 267 |

| Sable 140 — IDD7 Measurement-Loop Pattern                                               | . 271 |

| Table 141 — AC Timings                                                                  | . 276 |

| Table 142 — Latency Timings (Part 1) for GDDR7 DRAMs Supporting Implicit CAPARBLK_LAT . | . 287 |

| Table 143 — Latency Timings (Part 1) for GDDR7 DRAMs Supporting Explicit CAPARBLK_LAT . | . 288 |

| Sable 144 — Latency Timings (Part 2)                                                    | . 289 |

| Table 145 — Frequency Dependent AC Timings                                              | . 290 |

| Table 146 — Ball-Out Description                                                        | . 291 |

| Table 147 — Example Logical Signal to Physical Pin Mapping for DQ[9:0]                  | . 293 |

| Sable 148 — Static Logical Pin State in DQ Map Mode                                     | . 294 |

| Sable 149 — Package Parameters                                                          | . 296 |

| Table 150 — CA State at Initialization for 4-Channel Mode vs. 2-Channel Mode            | . 298 |

### **Graphics Double Data Rate 7 SGRAM Standard (GDDR7)**

From JEDEC Board Ballot JCB-24-02, formulated under the cognizance of the JC-42.1 sub-committee on Graphics RAMs (GDDRx), item 1860.99.

#### 1 Scope

This standard defines the Graphics Double Data Rate 7 (GDDR7) Synchronous Graphics Random Access Memory (SGRAM) specification, including features, functionality, package, and pin assignments.

The purpose of this standard is to define the minimum set of requirements for 16 Gb through 64 Gb x8 quad channel GDDR7 SGRAM devices. System designs based on the required aspects of this standard will be supported by all GDDR7 SGRAM vendors providing compatible devices. Some aspects of the GDDR7 standard such as AC timings and capacitance values were not standardized. Some features are optional and therefore may vary among vendors. In all cases, vendor data sheets should be consulted for specifics. This document was created based on some aspects of the GDDR6 Standard (JESD250) and other JEDEC device standards.

#### 2 Overview, Definitions, and Organization

#### 2.1 Features

- 4 separate independent channels with point-to-point interface for data, Command Address (CA), and clocks

- Common differential clock inputs WCK\_t/WCK\_c per channel for the data bus (DQ, DQE) and the CA bus

- Double Data Rate (DDR) Data bus (with regards to the WCK)

- High-speed data signaling using PAM3; low speed data signaling option for NRZ

- Single ended or differential Read clock (RCK) per channel

- Single Data Rate (SDR) CA bus (with regards to the WCK); NRZ input with single and multicycle commands

- ERR signal (PAM3 coded) for communicating WRCRC and CAPAR errors

- CA Parity (CAPAR) and CA Parity with command blocking (CAPARBLK)

- 16 internal banks per channel

- 32n prefetch architecture: 256 bit per array read or write access per channel

- Burst length: 16 Symbols (PAM3) or 32 (NRZ)

- Programmable READ and WRITE latency

- Command Address bus inversion (CABI)

- Command Address bus training: command address input monitoring by DQ signals

- Data read and write training via READ FIFO or LFSR

- READ FIFO pattern preload by LDFF command

- PRBS 11 or 15 with programmable seed for LFSR Training

- LFSR burst error counter for Write training

- Lane masking, inversion, and pattern shift for LFSR training

- Eye masking for LSFR or FIFO mode training

- ERR signal training

- CA Oscillator (CAOSC)

- Read/Write data transmission integrity secured by cyclic redundancy check

- READ/WRITE CRC on/off mode

- Programmable DQE latency and WRCRC2ERR latency

- On-chip temperature sensor with read-out

- Auto precharge option for each burst access

- Auto refresh (16k cycles) with all-bank and per-bank options

- Self Refresh, Sleep, Self Refresh Sleep and Hibernate Self Refresh Sleep modes

- Temperature Controlled Self Refresh rate

- Frequency change sequence and Dynamic Voltage Sequence (DVS) support including FDMR

- CSP command for Sleep to synchronous operation

- CSP feedback for confirmation that device received CSP command

- Info Read for device identification and status information

- On-die ECC with error severity reporting during Reads

- Refresh Management (RFM), Adaptive RFM and Directed RFM

- Post package repair support (hPPR)

- On-die termination (ODT)

- Impedance calibration with external reference resistor (120 Ohm)

- Programmable termination and driver strength offsets for DQ/DQE/RCK

- Internal VREF for data inputs and CA inputs with programmable levels

- 4-channel/2-channel mode configuration set at power-up with CA0\_A and CA0\_C

- 1.2 V +/- 0.036 V supply for device operation (VDD)

- 1.2 V +/- 0.036 V supply for I/O interface (VDDQ)

- 1.8 V + 0.108 V / 0.054 V supply for VPP

- 266 ball BGA package with 0.73 x 0.75 mm pitch

#### 2.2 Functional Description

The GDDR7 SGRAM is a high-speed dynamic random-access memory designed for applications requiring high bandwidth. The device's architecture consists of four byte wide fully independent channels. GDDR7 uses a 256b per read and write array access architecture and a DDR PAM3 interface to achieve high-speed operation. In PAM3 mode the byte consists of ten DQ and one DQE signal. See the *PAM3* section for details on high speed I/O signaling. GDDR7 also includes a NRZ I/O signaling mode for low power operation that has a byte definition that includes eight DQ and one DQE.

GDDR7 devices contain the following number of bits:

16 Gb has 17,179,869,184 bits

24 Gb has 25,769,803,776 bits

32 Gb has 34,359,738,368 bits

48 Gb has 51,539,607,552 bits

64 Gb has 68,719,476,736 bits

The GDDR7 SGRAM's high-speed interface is optimized for point-to-point connections to a host controller. On-die termination (ODT) is provided for all high-speed interface signals to eliminate the need for termination resistors in the system.

GDDR7 operates from a differential clock WCK\_t and WCK\_c. WCK is common to both Command Address (CA) and DQ buses.

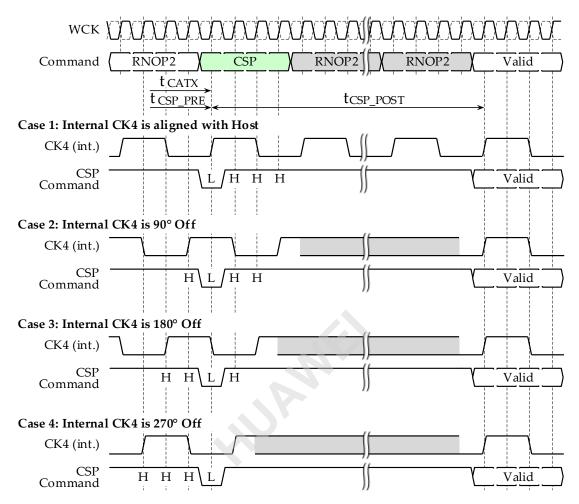

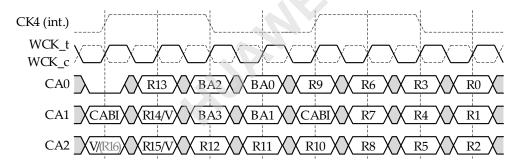

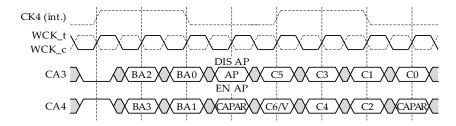

Command and Address (CA) are registered at every rising edge of WCK. GDDR7 uses a separate 4n-cycle (nCK4) Row Command bus and 4n-cycle (nCK4) Column Command bus. Row Command Address is 11-bit that contains command, bank address, row address, op code, and etc. via CA[2:0]. Column Command Address is 7-bit that contains command, bank address, column address, and etc. via CA[4:3]. There are both single nCK4 cycle and multi nCK4 cycle commands. See the *Command Truth Table* section for details.

The row and bank address to be accessed is registered coincident with the Activate command. The address bits registered coincident with the Read or Write command are used to select the bank and the starting column location for the burst access. Read and write accesses to GDDR7 are burst oriented; accesses start at a selected location and consists of a total of sixteen symbols in PAM3 mode and thirty-two data words in NRZ mode. Accesses begin with the registration of an Activate command, which is then followed by a Read or Write command.

GDDR7 include several features to improve the integrity of data including OD-ECC, CRC, hPPR, CA Parity, and CAPAR with Command Blocking. See the *DATA INTEGRITY* section for more details.

Prior to normal operation, the GDDR7 SGRAM is required to be initialized. The *INITIALIZATION* section provides detailed information covering device initialization.

This standard includes all features and functionality required for GDDR7 SGRAM devices both in PAM3 mode and NRZ mode. In many cases the GDDR7 specification describes the behavior of a single channel.

#### 2.3 Definition Of Signal State Terminology

GDDR7 SGRAM will be operated in both ODT Enable (terminated) and ODT Disable (unterminated) modes. For highest data rates it is recommended to operate in the ODT Enable mode. ODT Disable mode is designed to reduce power and may operate at reduced data rates. There exist situations where ODT Enable mode cannot be guaranteed for a short period of time, i.e., during power up.

Following are four terminologies defined for the state of a device (GDDR7 SGRAM or controller) signal during operation. The state of the bus will be determined by the combination of the device signal connected to the bus in the system. For example, in GDDR7 it is possible for the SGRAM signal to be tristate while the controller signal is HIGH or ODT. In both cases the bus would be HIGH if the ODT is enabled. For details on the device's signals and their function see the *SIGNALS* section.

#### Device signal level:

- HIGH: A device signal is driving the Logic "HIGH" state in NRZ mode and "+1" in PAM3 mode. See the *PAM3* section for more details on PAM3 levels.

- LOW: A device signal is driving the Logic "LOW" state in NRZ mode and "-1" in PAM3 mode.

- High-Z: A device signal is tristate.

- ODT: A device signal terminates with ODT setting, which could be terminating or tristate depending on Mode Register setting.

#### 2.4 Clocking

The GDDR7 SGRAM supports two operating modes for WCK frequency which differ in the DQ[9:0]/DQE to WCK clock frequency ratio. The GDDR7 SGRAM supports NRZ mode and PAM3 mode operating modes for WCK frequency which differ in the DQ[9:0]/DQE to WCK clock frequency ratio.

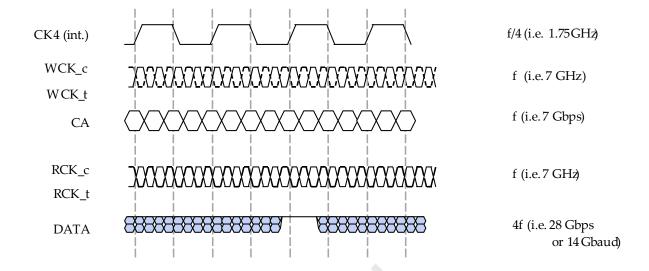

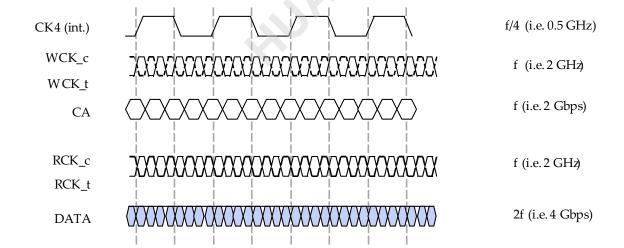

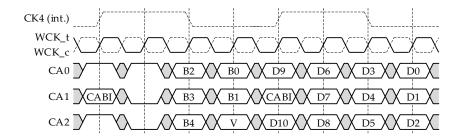

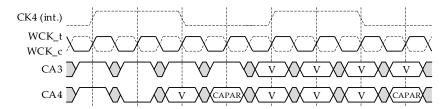

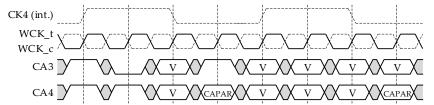

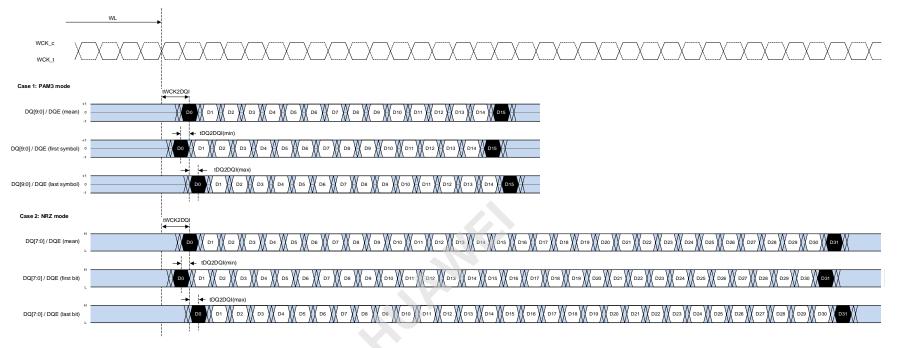

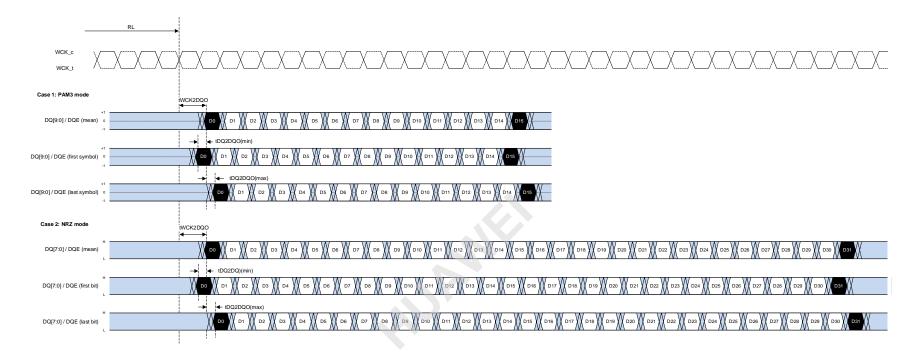

FIGURE 1 illustrates the difference between a NRZ mode and a PAM3 mode.

Each channel of a GDDR7 SGRAM includes a single differential clock pair WCK\_t/WCK\_c for latching command/address (CA) inputs, for latching write data and for driving read data. Command and Address (CA) are registered at every rising WCK edge.

A rising WCK edge is defined as the crossing of the positive edge of WCK\_t and the negative edge of WCK\_c. A falling WCK edge is defined as the crossing of the negative edge of WCK\_t and the positive edge of WCK\_c.

CK4 (int.) is quarter rate of WCK frequency for internal clocking and for AC timings. For commands that span multiple CK4 cycles the last CK4 cycle of a command is the reference point for all related AC timings and latencies. Timing diagrams are drawn accordingly.

Table 1 — Example of WCK and Interface Signal Frequency Relationship

| Signal                       | PAM3 mode | NRZ mode | UNIT      | Notes |

|------------------------------|-----------|----------|-----------|-------|

| CK4 (int)                    | 1.75      | 0.5-     | GHz       | 1     |

| WCK_t, WCK_c<br>RCK_t, RCK_c | 7         | 2        | GHz       |       |

| CA[4:0]                      | 7         | 2        | Gbps/pin  |       |

| DQ[7:0], DQE                 | -         | 4        | Gbps/pin  |       |

| DQ[7.0], DQE                 | 14        | -        | Gbaud/pin | 2     |

| DQ[9:8]                      | 14        | -        | Gbaud/pin | 2     |

NOTE 1 CK4 (int.) is an internal clock that is referenced e.g., by cycle based AC Timings and latencies.

NOTE 2 The 14 GBaud in PAM3 mode correspond to a data rate of 28 Gbps over 8 DQs or a per-channel memory bandwidth of 28 GB/s.

#### 2.4 Clocking (cont'd)

#### PAM3 mode

#### NRZ mode

Figure 1 — GDDR7 Clocking and Interface Relationship

#### 2.4 Clocking (cont'd)

The GDDR7 SGRAM supports two operating modes for WCK frequency which differ in the DQ[9:0]/DQE to WCK clock frequency ratio. The GDDR7 SGRAM supports NRZ mode and PAM3 mode operating modes for WCK frequency which differ in the DQ[9:0]/DQE to WCK clock frequency ratio.

FIGURE 1 illustrates the difference between a NRZ mode and a PAM3 mode.

Each channel of a GDDR7 SGRAM includes a single differential clock pair WCK\_t/WCK\_c for latching command/address (CA) inputs, for latching write data and for driving read data. Command and Address (CA) are registered at every rising WCK edge.

A rising WCK edge is defined as the crossing of the positive edge of WCK\_t and the negative edge of WCK\_c. A falling WCK edge is defined as the crossing of the negative edge of WCK\_t and the positive edge of WCK\_c.

CK4 (int.) is quarter rate of WCK frequency for internal clocking and for AC timings.

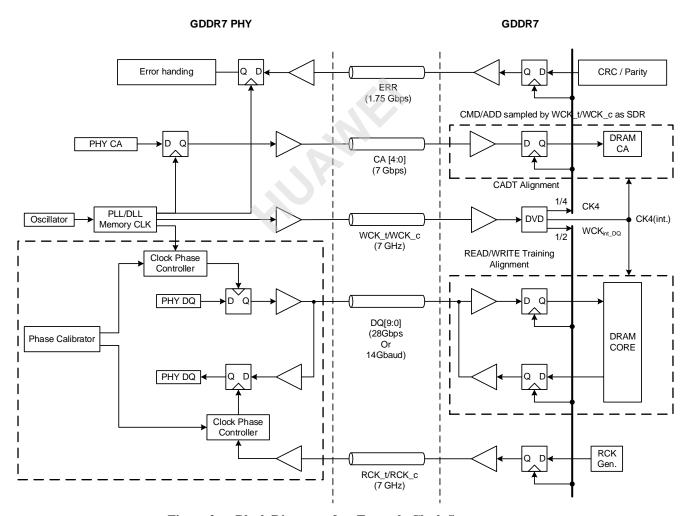

Figure 2 — Block Diagram of an Example Clock System

#### 2.5 Addressing

GDDR7 SGRAMs use a single data rate command address scheme on the device. The command and addresses is packetized on 5 CA signals (CA[4:0]) over either single CK4 cycle or multi CK4 cycles depending on the command (see *COMMAND TRUTH TABLE*).

To enable higher performance, GDDR7 SGRAMs provide semi-independent row and column command interfaces for each channel. These interfaces increase command bandwidth by allowing read and write commands to be issued simultaneously with other commands like Activate and Precharge commands. See *Row AND COLUMN COMMANDS*.

GDDR7 addressing is defined for a single channel with devices being configured to either 2 or 4 channels/device.

| Memory                                    | 16           | Gb           | 24           | Gb           | 32           | Gb           | 48           | Gb           | 64 Gb          |              |

|-------------------------------------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|----------------|--------------|

| Density                                   | 17,179,      | 869,184      | 25,769,      | 803,776      | 34,359,      | 738,368      | 51,539,      | 607,552      | 68,719,476,736 |              |

| Device<br>Organization                    | 4 CH<br>Mode | 2 CH<br>Mode | 4 CH<br>Mode   | 2 CH<br>Mode |

| Number<br>channels                        | 4            | 2            | 4            | 2            | 4            | 2            | 4            | 2            | 4              | 2            |

| <b>Channel Density</b>                    | 4 Gb         | 8 Gb         | 6 Gb         | 12 Gb        | 8 Gb         | 16 Gb        | 12 Gb        | 24 Gb        | 16 Gb          | 32 Gb        |

| Array Pre-Fetch<br>(bits, per<br>channel) | 256          |              | 256          |              | 256          |              | 256          |              | 256            |              |

| Bank address<br>(per channel)             | BA[3:0]      |              | BA[3:0]      |              | BA[3:0]      |              | BA[3:0]      |              | BA[3:0]        |              |

| Number Banks<br>(per channel)             | 16           |              | 16           |              | 16           |              | 16           |              | 16             |              |

| Row address<br>(per channel)              | R[13:0]      | R[14:0]      | R[14:0]      | R[15:0]      | R[14:0]      | R[15:0]      | TBD          | TBD          | TBD            | TBD          |

| Number of Rows<br>(per channel)           | 16,384       | 32,768       | 24,576       | 49,152       | 32,768       | 65,536       | TBD          | TBD          | TBD            | TBD          |

| Column address<br>(per channel)           | C[5:0]       | C[5:0]       | C[5:0]       | C[5:0]       | C[5:0]       | C[5:0]       | TBD          | TBD          | TBD            | TBD          |

| Page Size<br>(per channel)                | 2K           | 2K           | 2K           | 2K           | 2K           | 2K           | TBD          | TBD          | TBD            | TBD          |

Table 2 — Addressing Scheme

#### NOTES:

- 1. The column address notation for GDDR7 does not include addressing within the prefetch of 256 bits as the burst order is always fixed for READ and WRITE commands.

- 2. Page Size = 2^COLBITS \* (Prefetch\_Size/8) where COLBITS is the number of column address bits.

- 3. Row address range with R[15:14] = 11 for 2 CH mode and R[14:13] = 11 for 4 CH mode is not present for 24 Gb density.

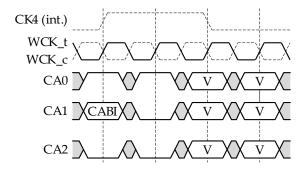

#### 2.6 Command Address Bus Inversion (CABI)

Command Address Bus Inversion (CABI) reduces the power requirements on Command Address (CA) bus, as the number of CA lines driving a LOW level can be limited to 10-bit in 20-bit of 4-cycle Row and Column CA per channel.

The Command Address Bus Inversion function is associated with the electrical signaling on the CA lines between a controller and the device, regardless of whether the information conveyed on the CA lines is a row or column address, a command, a mode register op-code, par, or any other pattern.

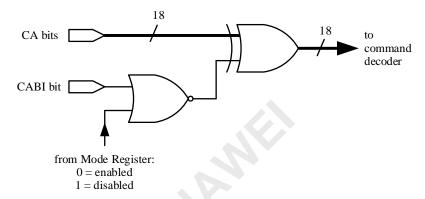

Once enabled by the corresponding CABI Mode Register bit, the GDDR7 SGRAM will invert the pattern received on the CA inputs in case CABI was sampled LOW, or leave the pattern non-inverted in case CABI was sampled HIGH, as shown in *FIGURE 3*. If CABI is disabled (MR0 OP0=1), CABI (CA1 of 0th clock cycle) bit is "Valid" (V) but it is recommended to be set to HIGH.

Figure 3 — Example of Command Address Bus Inversion Logic

#### 2.7 Command Address Parity (CAPAR) Definition

The convention of parity is even parity, i.e., valid parity is defined as an even number of ones across the inputs used for parity computation combined with the parity signal. In other words, the parity bit is chosen so that the total number of 1's in the 20-bit, including the parity bit is even. If CAPAR is disabled (MR15 OP0=0), CAPAR bit (CA4 of 3rd clock cycle) is "Valid" (V) but it is recommended to be set to HIGH. See the *Command Address Parity (CAPAR) Protocol* section for more details.

| '1' count | Command Address (19-bit) | CAPAR |

|-----------|--------------------------|-------|

| even      | 000 0000 0000 1111 1111  | LOW   |

| odd       | 000 0000 0001 1111 1111  | HIGH  |

**Table 3** — Example of CAPAR (Even Parity)

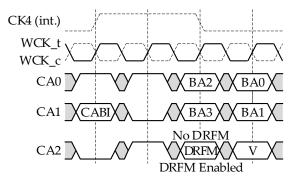

#### 2.8 CABI and CAPAR Order

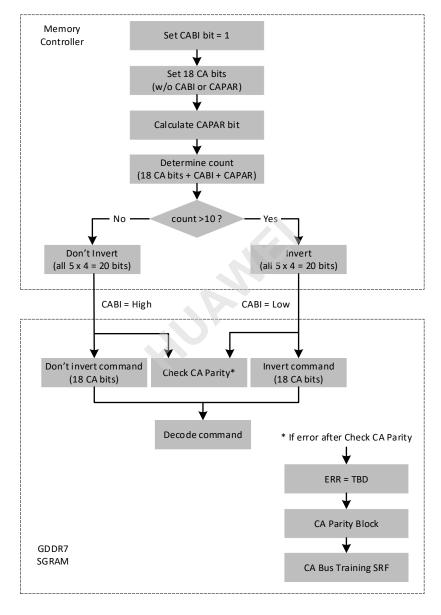

The flow diagram in *FIGURE 4* illustrates the CABI and CAPAR operation. The controller decides whether to invert or not invert the data conveyed and then make even parity with CAPAR on the CA lines. The GDDR7 SGRAM must perform the reverse operation based on even parity with CAPAR and the level of CABI. CA input timing parameters are only valid with CABI being enabled and a maximum of 9 CA inputs driven LOW in 4-cycle CA BUS.

- NOTE 1 18-bit is 4-cycle of CA bus excluding CABI (0<sup>th</sup> clock cycle CA1) and CAPAR (3<sup>rd</sup> clock cycle CA4)

- NOTE 2 CABI (MR0 OP0), CAPAR (MR015, OP0) and CAPARBLK (MR015 OP1) are enabled for illustration

- NOTE 3 If CABI and CAPAR are disabled, CABI bit & PAR bit are "Valid" (V) but they are recommended to be set to HIGH.

Figure 4 — Command Address Bus Inversion (CABI) and Command Address Parity (CAPAR)

Flow Diagram

#### 2.9 PAM3

#### 2.9.1 PAM3 Signaling and Encoding Conventions

The GDDR7 SGRAMs can be configured to use a PAM3 I/O system for the data interface (DQ[9:0], DQE). PAM3 works with point-to-point signaling between driver and receiver. PAM3 is enabled by setting MR0 OP8 to 1.

The PAM3 signaling transmits a ternary digit (or trit) per U.I. using three distinct signal levels in a balanced signed-digit representation (+1, 0, -1). Each PAM3 symbol is internally represented by two bits, although only three combinations are valid as shown in *TABLE 4*.

| Binary<br>[MSB:LSB]                                                                       | PAM3 Symbol<br>(Ternary Digit) | Nominal Voltage Level [%V <sub>DDQ</sub> ] <sup>1</sup> |  |  |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------|--------------------------------|---------------------------------------------------------|--|--|--|--|--|--|--|--|

| 1 1                                                                                       | +1                             | 100.0%                                                  |  |  |  |  |  |  |  |  |

| 1 0                                                                                       | Invalid                        | -                                                       |  |  |  |  |  |  |  |  |

| 0 1                                                                                       | 0                              | 75%                                                     |  |  |  |  |  |  |  |  |

| 0 0                                                                                       | -1                             | 50%                                                     |  |  |  |  |  |  |  |  |

| NOTE 1 Refer to the <i>Operating Conditions</i> Section for absolute VDDQ voltage levels. |                                |                                                         |  |  |  |  |  |  |  |  |

Table 4 — PAM3 Signal Levels

#### 2.9.2 PAM3 Burst Encoding

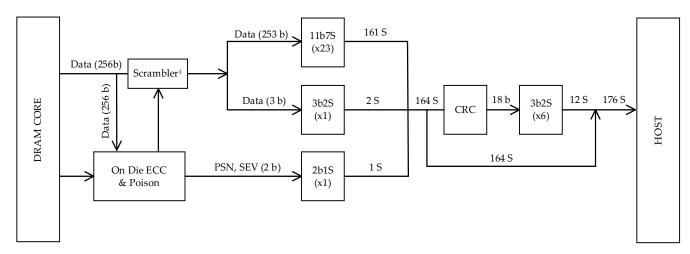

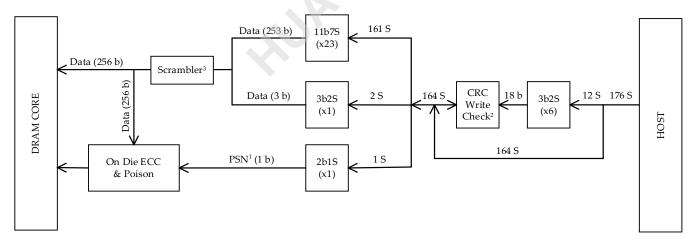

In PAM3 mode GDDR7 SGRAMs transfer a total of 176 symbols per burst access over 11 data lines (BL  $16 \times 11 \text{ DQs} = 176 \text{ Symbols}$ ). Write data is PAM3 decoded before written to the memory array, read data is PAM3 encoded before it is transmitted. The maximum burst data payload is 276 bits, as in the case of read direction when CRC and poison are enabled (256 data bits + 18 CRC bits + 1 Severity bit + 1 Poison bit).

To avoid CRC error multiplication, reduce static termination power and to maximize the relationship between encoding efficiency and implementation simplicity, the GDDR7 makes use of different types of PAM3 encoders/decoders, as shown in *FIGURE 5* and *FIGURE 6*.

- **11b7S**: eleven-bits-to-seven-symbols encoder/decoder for efficient data coding. The encoder/decoder truth table is shown in *TABLE 7* and a recommendation for efficient implementation of the encoder/decoder is provided and explained in *SECTION 2.9.3*.

- **3b2S**: three bits-to-two-symbols encoder/decoder for DC balanced encoding, as defined in *TABLE* 5. Instances of this encoder are used to encode the CRC (in PAM3 and NRZ modes), and in PAM3 mode for LFSR training and the 3 bits of data remainder on DQ4 (see *FIGURE 7*).

- **2b1S**: two-bits-to-1-symbol encoder/decoder for Severity and Poison, as in *TABLE 6*. Note that SEV/PSN are mutually exclusive, Severity prevails over Poison.

The total burst transfer payload per channel is encoded using 23 x 11b7S and 1 x 3b2S for the data, 6 x 3b2S for the CRC and 1 x 2b1S for the SEV/PSN, it adds up to the 176 PAM3 symbols that can be allocated for a 16 burst over 11 data lines. The logical to physical lane mapping, burst order and bit-to-symbol encoder grouping is shown in *FIGURE 7*.

#### 2.9 PAM3 (cont'd)

NOTE 1: The scrambler block performs a bitwise XOR operation on the array read data before PAM3 encoding using the scrambler code as programmed in MR20. Please refer to the STATIC DATA SCRAMBLER section for details.

Figure 5 —Burst Data Payload Encoding Diagram (Read Operation)

- NOTE 1 Severity flag is not transmitted during write operation.

- NOTE 2 During Writes, the DRAM computes the CRC on the received data and the result is compared with the 18 bits CRC received from the host, a mismatch is reported back to the host on the ERR pin as CRC Write Error.

- NOTE 3 The scrambler block performs a bitwise XOR operation on the data after PAM3 decoding before writing it to the array using the scrambler code as programmed in MR20. Please refer to the STATIC DATA SCRAMBLER section for details.

Figure 6 —Burst Data Payload Decoding Diagram (Write Operation)

### 2.9 PAM3 (cont'd)

Table 5 — 3b2S Encoder for CRC, Data Remainder, and LFSR Training

|            | 3b2S PAM3 Encoder/Decoder Truth Table |            |        |            |        |            |           |    |  |  |  |  |  |

|------------|---------------------------------------|------------|--------|------------|--------|------------|-----------|----|--|--|--|--|--|

|            | 3 Bits                                |            | Inter  | nal Binary | ation  | 2 Trits    |           |    |  |  |  |  |  |

| MSB        |                                       | LSB        | S1 MSB | S1 LSB     | S0 MSB | S0 LSB     |           |    |  |  |  |  |  |

| <b>b</b> 2 | b1                                    | <b>b</b> 0 | b3     | <b>b</b> 2 | b1     | <b>b</b> 0 | <b>S1</b> | SO |  |  |  |  |  |

| 0          | 0                                     | 0          | 0      | 1          | 0      | 0          | 0         | -1 |  |  |  |  |  |

| 0          | 0                                     | 1          | 0      | 0          | 1      | 1          | -1        | +1 |  |  |  |  |  |

| 0          | 1                                     | 0          | 1      | 1          | 0      | 0          | +1        | -1 |  |  |  |  |  |

| 0          | 1                                     | 1          | 0      | 1          | 1      | 1          | 0         | +1 |  |  |  |  |  |

|            | Invalid                               |            | 0      | 1          | 0      | 1          | 0         | 0  |  |  |  |  |  |

| 1          | 0                                     | 0          | 0      | 0          | 0      | 0          | -1        | -1 |  |  |  |  |  |

| 1          | 0                                     | 1          | 0      | 0          | 0      | 1          | -1        | 0  |  |  |  |  |  |

| 1          | 1                                     | 0          | 1      | 1          | 0      | 1          | +1        | 0  |  |  |  |  |  |

| 1          | 1                                     | 1          | 1      | 1          | 1      | 1          | +1        | +1 |  |  |  |  |  |

Table 6 — Severity and Poison 2b1S Encoder/Decoder

| 2b1S PAM3 Encoder/Decoder for SEV/PSN |     |    |            |    |  |  |  |  |  |  |  |

|---------------------------------------|-----|----|------------|----|--|--|--|--|--|--|--|

| 2 Bits Binary 1 Trit                  |     |    |            |    |  |  |  |  |  |  |  |

| SEV                                   | PSN | b1 | <b>b</b> 0 | S0 |  |  |  |  |  |  |  |

| 1                                     | X   | 0  | 0          | -1 |  |  |  |  |  |  |  |

| 0                                     | 1   | 0  | 1          | 0  |  |  |  |  |  |  |  |

| 0                                     | 0   | 1  | 1          | +1 |  |  |  |  |  |  |  |

NOTE 1 During read operation Severity has precedence over Poison, therefore Poison flag is "don't care" when Severity flag is set. During write operation SEV flag is always 0, hence only +1 and 0 input levels are allowed.

NOTE 2 MR0 OP9 (Severity) shall be turned on when MR0 OP10 (Poison) is enabled. When Poison is enabled, it is enabled for both RD and WR operations. When Poison and/or Severity are disabled, their default value will be set to '0'.

### 2.9 PAM3 (cont'd)

Table 7 — 11b7S Encoder/Decoder Table

| 11b     | 7S      | 11b     | <b>7</b> S | 11b     | <b>7</b> S | 11b     | 7S      | 11b     | 7S      | 11b     | <b>7</b> S | 11b     | 7S      | 11b     | 7S      |

|---------|---------|---------|------------|---------|------------|---------|---------|---------|---------|---------|------------|---------|---------|---------|---------|

| b[10:0] | b[13:0] | b[10:0] | b[13:0]    | b[10:0] | b[13:0]    | b[10:0] | b[13:0] | b[10:0] | b[13:0] | b[10:0] | b[13:0]    | b[10:0] | b[13:0] | b[10:0] | b[13:0] |

| 0x000   | 0x447   | 0x100   | 0x1047     | 0x200   | 0xc47      | 0x300   | 0x3047  | 0x400   | 0x1447  | 0x500   | 0x3447     | 0x600   | 0x1c47  | 0x700   | 0x3c47  |

| 0x001   | 0x444   | 0x101   | 0x1044     | 0x201   | 0xc44      | 0x301   | 0x3044  | 0x401   | 0x1444  | 0x501   | 0x3444     | 0x601   | 0x1c44  | 0x701   | 0x3c44  |

| 0x002   | 0x445   | 0x102   | 0x1045     | 0x202   | 0xc45      | 0x302   | 0x3045  | 0x402   | 0x1445  | 0x502   | 0x3445     | 0x602   | 0x1c45  | 0x702   | 0x3c45  |

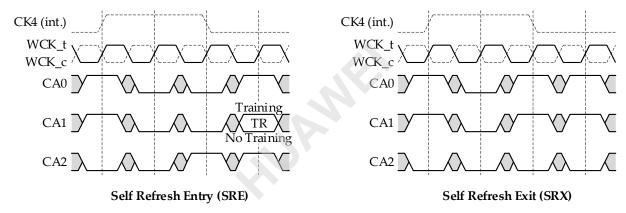

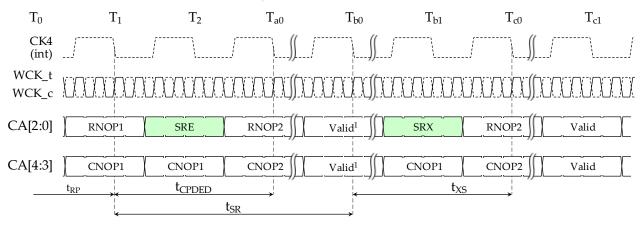

| 0x003   | 0x441   | 0x103   | 0x1041     | 0x203   | 0xc41      | 0x303   | 0x3041  | 0x403   | 0x1441  | 0x503   | 0x3441     | 0x603   | 0x1c41  | 0x703   | 0x3c41  |