80586-初代奔腾的超标量

初代奔腾,是第五代宏内核x86架构之微处理器,于1993年3月22日开始出货。他是486产品线的后代。Pentium本应命名为80586或i586,后来命名为"Pentium"(通常认为i586被使用在英特尔竞争对手所制造的类80586的微处理器。

超标量(Superscalar)架构

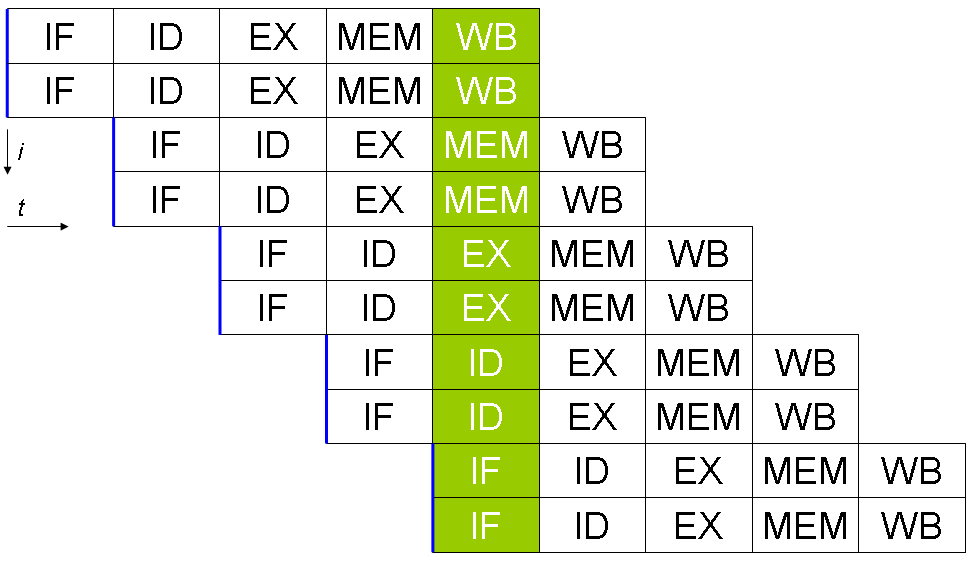

CPU发展到486以后,计算单元已经不仅限于ALU,而是有一些其他们的单元,分别负责不同的运算类型,比如说算术逻辑单元(ALU)、乘法器、移位器等。这些单元是可以独立工作的。在只有一个pipeline的时候,同一个时钟cpu只能解码一条指令,那么虽然有多个单元,但同时只能有一个单元在工作,就是很浪费的。所以P5上,CPU有两个pipe line,可以同时取指两个指令、同时解码两个指令、同时执行两个指令(如果它们可以被分配在不同的计算单元上话)。

Pentium拥有两个数据路径(管线,pipelines),可以达到在一个时钟周期内完成一个以上的指令。一个管线(称为"U")可以处理任何的指令,而另外一个(称为"V")可以处理简单的整数及FXCH浮点数指令。使用一个以上的管线是传统RISC处理器设计的特色,这也是在许多x86平台上第一个实现出来的,显示有将两种技术合并的可能性,创造出几乎"混合在一起"的处理器。

如图所示: pentium处理器内部有两组取指、译码、地址生成部件、并且是两组L1 cache,均是8KB。它还有两个ALU,可以用来同时执行两条指令。但是它只有一组浮点运算部件,所以如果取到的两条指令都是浮点指令,就没有办法同时执行了。

超标量并不是超线程,超线程要求同一个核心有两套执行部件的同时,还有两套保存线程状态的寄存器。超标量是没有的,所以它不能同时执行两个线程上的两个指令,只能执行同一个线程上的两个指令。这两个指令不必是连续,可以是cpu硬件分析出来的一段代码中两个互相不依赖结果的任意指令。也就是说ABCD四条指令,要求CPU能够分析出C指令的执行不依赖AC的结果,所以C指令可以先于B指令在另一个ALU上计算也不影响程序的最终结果。这时就可以A,C两条指令同时执行。这个打乱指令执行顺序的过程叫做乱序执行。乱序执行一般要求有一个部件叫做ROB, reorder buffer,即一个分析指令可以如何乱序的缓冲区,但上图中并没有画,上图中的ROM控制部件我十分怀疑是画错了,也许就是ROB控制部件。